# COMS10015 hand-out: exam-style revision questions

# Part I: Mathematical preliminaries

$\triangleright$  **Q1.** We studied representation of unsigned integers using a base-*b* positional number system. Which of the following literals

A: 10101

B: 11111

C: 11120

D: 12200

E: 12345

represents the unsigned decimal integer 123<sub>(10)</sub> in base-3 (or ternary, digits in which are termed trits).

$\triangleright$  **Q2.** Imagine that two signed, 8-bit integers x and y are represented using two's-complement and sign-magnitude respectively, and both of which have the decimal value  $51_{(10)}$ . If the most-significant bit of both x and y is set to 1, what are their new (decimal) values?

A:  $-77_{(10)}$  and  $179_{(10)}$

B:  $-77_{(10)}$  and  $-51_{(10)}$

C:  $-51_{(10)}$  and  $-77_{(10)}$

D: 179<sub>(10)</sub> and 179<sub>(10)</sub>

E: 179<sub>(10)</sub> and -51<sub>(10)</sub>

$\triangleright$  **Q3.** Imagine that two signed, 16-bit integers x and y are represented using two's-complement; their product  $r = x \cdot y$  is a signed, 32-bit integer also represented using two's-complement. What is the largest (i.e., whose magnitude is greatest) negative value of r possible?

A: -0

B: -32768

C: -65535

D: -1073709056

E: -2147483648

$\triangleright$  **Q4.** Imagine you write a C program that defines signed, 16-bit integer variables **x** and **y** (of type short) and then assigns them the decimal values  $256_{(10)}$  and  $4852_{(10)}$  respectively. If **x** and **y** are then cast into signed, 8-bit integers (of type char), which of the following

A: 0 and 12

B: 0 and -12

C: -1 and 256

D: -1 and -52

E: 0 and 52

identifies their decimal value? Or, put another way, which are the result of evaluating the two expressions ( char )( x ) and ( char )( y )?

$\triangleright$  **Q5.** Consider two signed, 8-bit integer variables x and r (of type char) used in a C program. If x has the decimal value  $9_{(10)}$  and an assignment

$$r = ( \sim x << 4 ) 0x97$$

is executed, what is the decimal value of r afterwards?

$A: -9_{(10)}$

- $B: -1_{(10)}$

- $C: O_{(10)}$

- $D: 1_{(10)}$

- $E: 9_{(10)}$

$\triangleright$  **Q6.** In general, some x is a fixed point of a function f if f(x) equals x, i.e., if f maps x to itself. Consider the following function

```

int8_t abs( int8_t x ) {

int8_t r;

if( x >= 0 ) {

r = x;

}

else {

r = -x;

}

return r;

}

```

implemented in C: abs was written in an attempt to compute the absolute value of x, a signed, 8-bit integer representing using two's-complement. How many of the  $2^8 = 256$  possible values of x are fixed points of abs?

- A: 0

- B: 127

- C: 128

- D: 129

- E: 256

- $\triangleright$  **Q7.** Imagine that within a given C function, you declare signed, 8-bit integer variables (i.e., variables whose type is int8\_t) x and r. Assume C represents signed integers using two's-complement, and the right-shift operator yields arithmetic (rather than logical) shift: if x has the (decimal) value  $-10_{(10)}$ , what (decimal) value does r have after the assignment

$$r = \sim ((x >> 2) ^{0.0} 0xF4)$$

is executed?

- $A: -10_{(10)}$

- B:  $10_{(10)}$

- $C: 11_{(10)}$

- $D: 54_{(10)}$

- $E: 203_{(10)}$

- $\triangleright$  **Q8.** Consider two unsigned, 8-bit integer variables, x and y, as declared in some C function by using the type uint8\_t. For how many assignments to these variables will the Hamming weight of their unsigned, 8-bit integer sum, i.e., x + y, be zero? Put another way, how many elements does the set

$$\{(x,y) \mid HW(x + y) = 0\}$$

have?

- A: 0

- B: 1

- C: 255

- D: 256

- E: 65536

- $\triangleright$  **Q9.** Consider a literal  $\hat{x} = 10$ , which represents a value x using a base-b positional number system. Based on this information alone, which of the following values

- **A:** x = 1

- B: x = 2

- C: x = b

- D: x = 10

- **E**: x = 16

is correct?

$\triangleright$  **Q10.** Assuming an *n*-bit *x* and use of two's-complement representation for signed integers, which of the following identities

- A:  $x \land \neg x \equiv 0_{(10)}$

- B:  $x \lor \neg x \equiv -1_{(10)}$

- C:  $x \oplus \neg x \equiv -1_{(10)}$

- D:  $x + \neg x \equiv -1_{(10)}$

- E:  $x \neg x = -1_{(10)}$

is **not** correct?

- ▷ Q11. Classify each of the following statements as either true or false, then explain why using at most a few sentences.

- a If HW(x) and HD(x, y) denote Hamming weight (of x) and Hamming distance (between x and y), one can define  $HD(x, y) = HW(x \oplus y)$ .

- b If an *n*-bit integer x is represented using two's-complement, setting x = -1 implies setting each bit in the representation of x to 1.

- $\triangleright$  **Q12.** a For the sets  $A = \{1, 2, 3\}$ ,  $B = \{3, 4, 5\}$  and  $\mathcal{U} = \{1, 2, 3, 4, 5, 6, 7, 8\}$ , compute the following:

- i |A|.

- ii  $A \cup B$ .

- iii  $A \cap B$ .

- iv A B.

- $v \overline{A}$ .

- vi  $\{x \mid 2 \cdot x \in \mathcal{U}\}.$

- b For each of the following decimal integers, write down the 8-bit binary representation in sign-magnitude **and** two's-complement:

- i +0.

- ii -0.

- iii +72.

- iv −34.

- v -8.

- vi 240.

- $\triangleright$  **Q13.** For some 32-bit integer x, explain what is meant by the Hamming weight of x; write a short C function to compute the Hamming weight of a given 32-bit input.

- $\triangleright$  **Q14.** From the following list

- A:  $(x \wedge y) \oplus z$

- B:  $(\neg x \lor y) \oplus z$

- C:  $(x \lor \neg y) \oplus z$

- D:  $\neg(x \lor y) \oplus z$

- E:  $\neg \neg (x \lor y) \oplus z$

identify **each** Boolean expression that evaluates to 1 given the assignment x = 0, y = 0 and z = 1.

### **Description Description Description One** of the following equivalences

A:

$$(x \wedge y) \wedge z \equiv x \wedge (y \wedge z)$$

B:

$$x \lor 1 \equiv x$$

C:

$$x \vee \neg x \equiv 1$$

D:

$$\neg(x \lor y) \equiv \neg x \land \neg y$$

E:

$$\neg \neg x \equiv x$$

is incorrect: identify which.

### **> Q16.** The Boolean expression

$$(x \lor (z \lor y)) \land \neg(\neg y \land \neg z)$$

is equivalent to which of the following alternatives?

A:

$$y \lor z$$

B:

$$((x \lor z) \lor y)) \land (x \lor z)$$

C:

$$(x \land y) \lor (x \land z)$$

D:

$$(x \lor y) \land \neg(x \lor z)$$

$$E: (x \wedge z) \vee (x \wedge y)$$

### ⊳ **Q17.** The Boolean expression

$$(x \lor y) \lor (x \land z)$$

is equivalent to which of the following alternatives?

A:

$$(x \lor y) \land (x \lor z)$$

B:

$$(x \lor y) \land z$$

$$C: (x \vee y) \wedge (x \wedge z)$$

$$D: x \vee y$$

E:

$$(x \wedge y) \vee x$$

**> Q18.** A given set of Boolean operators may be termed functionally complete (or universal): this means *any* Boolean function can be expressed using a Boolean expression involving elements of the set alone. For example, because we know the NAND operator is functionally complete, we can also term the sets  $\{ \overline{\land} \}$  and  $\{ \land, \neg \}$  functionally complete. Noting that  $\not\equiv$  and  $\Rightarrow$  denote the inverse of equivalence and implication respectively (i.e., not equivalent, and does not imply), which of the following sets

$$A: \{\oplus, \vee\}$$

$$B: \{ \Rightarrow, \neq \}$$

D: all of the above

E: none of the above

is/are functionally complete?

$\triangleright$  **Q19.** How many *n*-input, 1-output Boolean functions are there?

- A: 1

- B: n

- C:  $2^{n}$

- D:  $2^{2^n}$

- E:  $2^{2^{2^n}}$

### ⊳ **Q20.** Consider the equivalence

$$(y \land \neg x) \lor (x \land \neg y) \equiv (x \lor y) \land \neg (x \land y),$$

the LHS of which can be manipulated into the RHS by applying the following sequence of Boolean axioms:

identity  $\sim$  inverse  $\sim$  distribution  $\sim$  commutativity  $\sim$  distribution  $\sim$  commutativity  $\sim$  X

The final axiom is missing, i.e., replaced with X: which of the following options for X yields a valid derivation?

- A: Absorption

- B: Idempotency

- C: Implication

- D: Null

- E: de Morgan

### ▷ **Q21.** One of the following equivalences

A:

$$(x \wedge y) \wedge z \equiv x \wedge (y \wedge z)$$

B:

$$x \Rightarrow y \equiv \neg x \lor y$$

C:

$$x \land (x \lor y) \equiv y$$

D:

$$\neg(x \lor y) \equiv \neg x \land \neg y$$

$$E: x \vee 0 \equiv x$$

is incorrect: identify which.

### ▷ **Q22.** Identify which of the following Boolean expressions

A:

$$x \wedge (x \vee \neg x)$$

B:

$$(x \lor \neg x) \land x$$

C: x

D: ¬⊅

$$E: \neg((\neg x \vee \neg x) \wedge (\neg x \vee x))$$

is **not** equivalent to

$$x \wedge x \vee x \wedge \neg x$$

.

#### $\triangleright$ **Q23.** Consider the following truth table, which describes a Boolean function f:

| w | х | y | Z | f(w, x, y, z) |

|---|---|---|---|---------------|

| 0 | 0 | 0 | 0 | 1             |

| 0 | 0 | 0 | 1 | 0             |

| 0 | 0 | 1 | 0 | 1             |

| 0 | 0 | 1 | 1 | 1<br>0<br>0   |

| 0 | 1 | 0 | 0 | 0             |

| 0 | 1 | 0 | 1 | 0             |

| 0 | 1 | 1 | 0 | 0             |

| 0 | 1 | 1 | 1 | 0<br>0        |

| 1 | 0 | 0 | 0 | 1             |

| 1 | 0 | 0 | 1 | 1             |

| 1 | 0 | 1 | 0 | 1<br>0        |

| 1 | 0 | 1 | 1 | 0             |

| 1 | 1 | 0 | 0 | 1             |

| 1 | 1 | 0 | 1 | 1<br>0        |

| 1 | 1 | 1 | 0 | 0             |

| 1 | 1 | 1 | 1 | 0             |

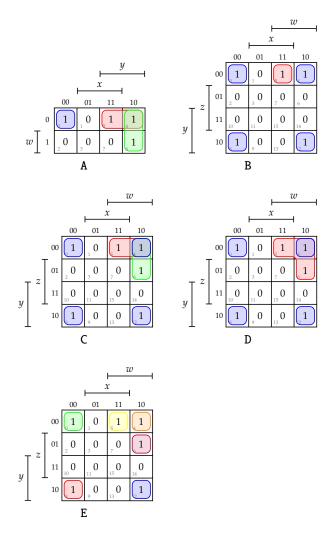

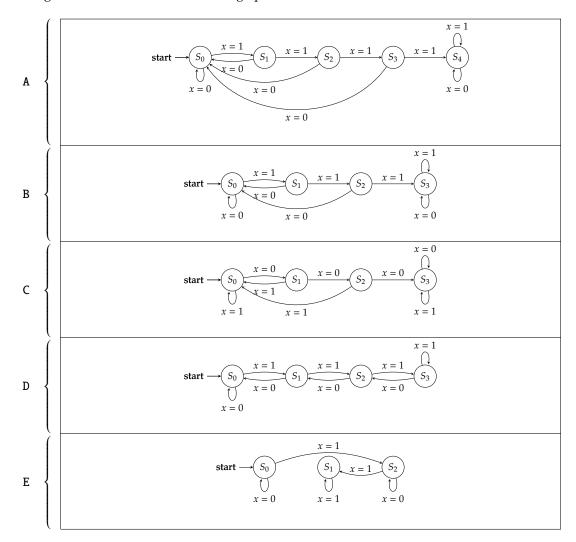

Which of the Karnaugh maps shown in Figure 1 will yield the most efficient (in terms of the number of operators involved), correct Boolean expression for *f*?

**Figure 1:** *A set of* 5 *different Karnaugh maps, captioned with an associated option.*

▷ **Q24.** Identify which of the following Boolean expressions

A:  $x \wedge y$

B:  $x \wedge z$

$C: y \wedge z$

D:  $x \wedge y \wedge z$

E: 1

is equivalent to

$$x \wedge y \vee x \wedge y \wedge z$$

.

$\triangleright$  **Q25.** Consider a Boolean function f with n = 1 input x. How many such functions are **not** idempotent, i.e., how many f exist such that  $\forall x \in \{0,1\}$ , f(f(x)) = f(x) does **not** hold?

A: 0

B: 1

C: 2

D:3

E: 4

$\triangleright$  **Q26.** Consider a Boolean function f with n=2 inputs x and y. How many such functions are symmetric, i.e., how many f exist such that  $\forall x, y \in \{0,1\}$ , f(x,y) = f(y,x) holds?

A: 0

- B: 1

- C: 2

- D: 8

- E: 16

- ▷ **Q27.** Which of the following Boolean expressions

- A:  $x \land \neg x \lor y \land (1 \lor x)$

- B:  $0 \lor x \land y \lor y$

- $C: x \wedge y$

- D: y

- E:  $\neg((\neg x \lor (x \land \neg y)) \land \neg y)$

is **not** equivalent to

$$x \wedge (\neg x \vee y) \vee y$$

.

- ▷ **Q28.** Which of the following Boolean expressions

- $A: \neg x$

- B: *x*

- C: ¬1/

- D: y

- E: 0

is equivalent to

$$(x \lor y) \land (x \lor \neg y).$$

- ▷ Q29. Classify each of the following statements as either true or false, then explain why using at most a few sentences.

- a A Boolean function  $f: \{0,1\}^2 \to \{0,1\}$  will require at least 1 Boolean operator to implement it.

- b Consider the concepts of disjunction and conjunction in Boolean algebra (i.e., that involving truth values); said concepts are analogous to those of addition and multiplication in elementary algebra (i.e., that involving numerical values).

- ⊳ **O30.** a Write out a truth table for the Boolean function

$$f(a,b,c) = (a \land b \land \neg c) \lor (a \land \neg b \land c) \lor (\neg a \land \neg b \land c),$$

then decide how many

- i input combinations, and

- ii outputs where f(a, b, c) = 1

exist in it.

b Consider the Boolean function

$$f(a,b,c,d) = \neg a \wedge b \wedge \neg c \wedge d.$$

Which of the following assignments

- i a = 0, b = 0, c = 0 and d = 1,

- ii a = 0, b = 1, c = 0 and d = 1,

- iii a = 1, b = 1, c = 1 and d = 1,

- iv a = 0, b = 0, c = 1 and d = 0.

produces the output f(a, b, c, d) = 1?

- c Which of the following Boolean expressions

- i  $(a \lor b \lor d) \land (\neg c \lor d)$ ,

- ii  $(a \wedge b \wedge d) \vee (\neg c \wedge d)$ ,

```

iii (a \lor b \lor d) \lor (\neg c \lor d).

```

is in Sum-of-Products (SoP) standard form?

d Identify each equivalence that is correct:

- i  $a \lor 1 \equiv a$ . ii  $a \oplus 1 \equiv \neg a$ .

- iii  $a \wedge 1 \equiv a$ .

- iv  $\neg (a \land b) \equiv \neg a \lor \neg b$ .

e Identify each equivalence that is correct:

- i  $\neg \neg a \equiv a$ .

- ii  $\neg (a \land b) \equiv \neg a \lor \neg b$ .

- iii  $\neg a \wedge b \equiv a \wedge \neg b$ .

- iv  $\neg a \equiv a \oplus a$ .

$\triangleright$  **Q31.** a The OR form of the null axiom is  $x \lor 1 \equiv 1$ . Which of the following options

- $i \quad x \wedge 1 \equiv 1$

- ii  $x \wedge 0 \equiv 0$ ,

- iii  $x \lor 0 \equiv 0$ ,

- iv  $x \wedge x \equiv x$ ,

is the dual of this axiom?

b Given the Boolean equation

$$f = \neg a \land \neg b \lor \neg c \lor \neg d \lor \neg e$$

which of the following

i

$$\neg f = a \lor b \lor c \lor d \lor e$$

,

ii

$$\neg f = a \land b \land c \land d \land e$$

,

iii

$$\neg f = a \land b \land (c \lor d \lor e)$$

,

iv

$$\neg f = a \land b \lor \neg c \lor \neg d \lor \neg e$$

,

$$\mathbf{v} \neg f = (a \lor b) \land c \land d \land e$$

is correct?

- c If we write the de Morgan axiom in English, which of the following

- i NOR is equivalent to AND if each input to AND is complemented,

- ii NAND is equivalent to OR if each input to OR is complemented,

- iii AND is equivalent to NOR if each input to NOR is complemented, or

- iv NOR is equivalent to NAND if each input to NAND is complemented.

describes the correct equivalence?

⊳ Q32. a Identify which one of these Boolean expressions

- i  $c \lor d \lor e$

- ii  $\neg c \land \neg d \land \neg e$

- iii  $\neg a \land \neg b$

- iv  $\neg a \land \neg b \land \neg c \land \neg d \land \neg e$

is the correct result of simplifying

$$(\neg(a \lor b) \land \neg(c \lor d \lor e)) \lor \neg(a \lor b).$$

b If you simplify the Boolean expression

$$(a \lor b \lor c) \land \neg (d \lor e) \lor (a \lor b \lor c) \land (d \lor e)$$

into a form that contains the fewest operators possible, which of the following options

i

$$a \lor b \lor c$$

,

```

ii \neg a \land \neg b \land \neg c,

iii d \lor e,

iv \neg d \land \neg e,

v none of the above

do you end up with and why?

c If you simplify the Boolean expression

a \wedge c \vee c \wedge (\neg a \vee a \wedge b)

into a form that contains the fewest operators possible, which of the following options

i (b \wedge c) \vee c,

ii c \lor (a \land b \land c),

iii a \wedge c,

iv a \lor (b \land c),

v none of the above

do you end up with and why?

d Consider the Boolean expression

a \wedge b \vee a \wedge b \wedge c \vee a \wedge b \wedge c \wedge d \vee a \wedge b \wedge c \wedge d \wedge e \vee a \wedge b \wedge c \wedge d \wedge e \wedge f.

Which of the following simplifications

i a \wedge b \wedge c \wedge d \wedge e \wedge f,

ii a \wedge b \vee c \wedge d \vee e \wedge f,

iii a \lor b \lor c \lor d \lor e \lor f,

iv a \wedge b,

v c \wedge d,

vi e \wedge f,

vii a \lor b \land (c \lor d \land (e \lor f))

viii ((a \lor b) \land c) \lor d \land e \lor f

is correct?

e Given the options

i 1,

ii 2,

iii 3,

iv 4,

decide which is the least number of operator required to compute the same result as

f(a,b,c) = (a \land b) \lor a \land (a \lor c) \lor b \land (a \lor c).

Show how you arrived at your decision.

f Prove that

(\neg x \land y) \lor (\neg y \land x) \lor (\neg x \land \neg y) \equiv \neg x \lor \neg y.

```

g Prove that

$$(x \wedge y) \vee (y \wedge z \wedge (y \vee z)) \equiv y \wedge (x \vee z).$$

h Simplify the Boolean expression

$$\neg (a \lor b) \land \neg (\neg a \lor \neg b)$$

into a form which contains the fewest operators possible.

# Part II: Basics of digital logic: general

$\triangleright$  **Q33.** From the following list

A: has N-type semiconductor terminals and P-type body

B: has P-type semiconductor terminals and N-type body

C: is paired with another N-MOSFET to form a CMOS cell

D: has a threshold voltage above which the transistor is deemed active

identify each statement that correctly describes an N-MOSFET.

### ▷ **Q34.** Consider the following implementation of a 2-input NAND gate:

### From the following list

A: two inputs x and y, and one output r

B: a pull-up network of P-MOSFET transistors

C: a pull-down network of BJT transistors

D: two power rails supplying different voltage levels

E: a flux capacitor

identify each component evident in the implementation?

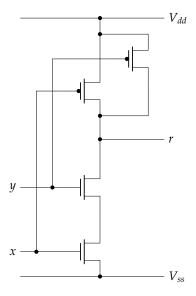

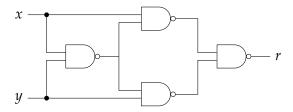

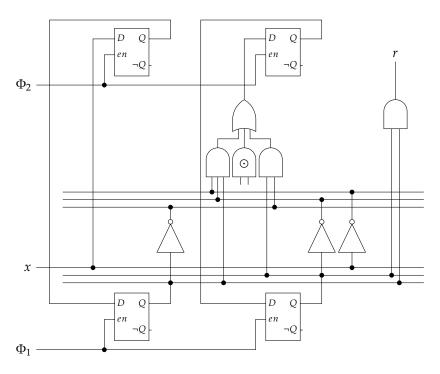

## ▷ Q35. Consider the following organisation of MOSFET transistors

which implements a 3-input Boolean function r = f(x, y, z). Which function, from the following, do you think it matches?

A:  $r = x \wedge y \wedge z$

B: r = x

$C \colon r = \neg(x \land (y \lor z))$

$D: r = x \wedge (y \vee z)$

E:  $r = x \lor y \lor z$

▶ Q36. Recall that a 2-input XOR operator can be described via the following truth table:

| y | r |

|---|---|

| 0 | 0 |

| 1 | 1 |

| 0 | 1 |

| 1 | 0 |

|   | 0 |

An implementation of this operator is realised by combining logic gate instances, e.g., for NOT, NAND, AND, NOR, and OR, while attempting to minimise the total number of underlying MOSFET-based transistors. How many such transistors do you think it uses?

A: 14

B: 16

C: 18

D: 20

E: 22

$\triangleright$  **Q37.** A buffer can be described as a "pass through" logic gate: although it performs no computation (i.e., the output r matches the input x, so r = x), it does impose a delay (often roughly the same as a NOT gate). It may be termed a non-inverting buffer (cf. an *inverting* buffer, or NOT gate) because of this.

You are asked to implement a buffer, using an unconstrained organisation of N- and P-MOSFET transistors alone. Assuming you attempt to minimise the number used, how many transistors do you need?

- **A**: 0

- B: 2

- C: 4

- D: 6

- E: 8

- ▷ Q38. Recalling that ? denotes don't-care, the following truth table

|   | f | c |        |

|---|---|---|--------|

| x | y | z | r      |

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 1      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 0      |

| 1 | 0 | 1 | 1<br>? |

| 1 | 1 | 0 | ?      |

| 1 | 1 | 1 | 1      |

describes a 3-input, 1-output Boolean function f st. r = f(x, y, z). Which of the following Boolean expressions

- A:  $(\neg x \oplus \neg y) \land z$

- B:  $(\neg x \oplus \neg y) \lor z$

- C:  $(\neg x \land \neg y) \land z$

- D:  $(\neg x \land \neg y) \lor z$

- **E**:  $(\neg x \lor \neg y) \land z$

correctly realises f?

- ▶ Q39. Imagine you want to design an 8-input, 8-bit multiplexer. Rather than do so from scratch, you intend to form the design using multiple instances of an existing 2-input, 1-bit multiplexer component. How many do you need?

- A: 1

- B:8

- C: 24

- D: 40

- E: 56

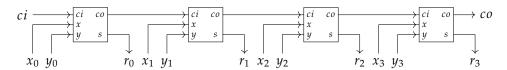

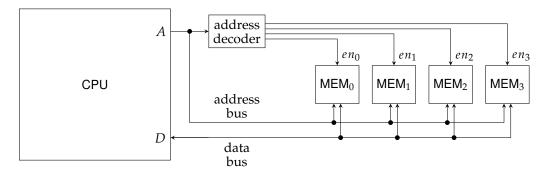

- **> Q40.** The following diagram

illustrates a 4-bit ripple-carry adder circuit, constructed using 4 full-adder instances: it computes the sum r = x + y + ci, given two operands x and y and a carry-in ci, and an associated carry-out co. Given the propagation delay of NOT, AND, OR and XOR gates is 10ns, 20ns, 20ns and 60ns respectively, which of the following

A: 120ns

B: 180ns

C: 240ns

D: 280ns

E: 480ns

most accurately reflects the critical path of the entire circuit?

Description > Q41. Imagine you use the ripple-carry adder in the previous question to compute an unsigned addition within some larger circuit. Having seen your design, your friend suggests they can optimise it: they claim that replacing each full-adder instance with a half-adder instance will halve the total number of logic gates required. However, they admit the optimisation does have a disadvantage. Specifically, although any value of *x* can be accommodated the optimised circuit can only produce the correct output for *some* values of *y*. Which of the following values of *y*.

A: -1

B: 0

C: 1

D: any  $2 \le y < 8$

**E:** any  $8 \le y < 16$

will produce the correct output?

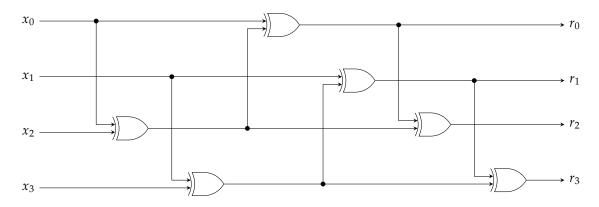

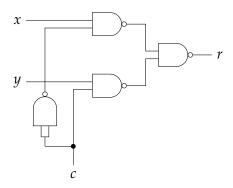

⊳ Q42. Consider the following combinatorial circuit

with a 4-bit input x and a 4-bit output r. Which of the following best describes the purpose of this circuit?

A: it computes the Hamming weight of x

B: it computes the parity of *x*

C: it swaps the most-significant 2-bit half of x with the least-significant 2-bit half of x

D: it adds the most-significant 2-bit half of *x* to the least-significant 2-bit half of *x* (treating it as an unsigned, 4-bit integer)

E: it negates x (treating it as a signed, 4-bit integer represented using two's-complement)

- ⊳ Q43. Recalling that ? denotes don't-care, consider the truth table shown in Figure 2.

- a Construction of a Karnaugh map for *f* demands formation of a set of groups; these (collectively) cover of all 1 entries. Assuming the most efficient approach is adopted when forming said groups, how many are required?

- A: 1

- B: 2

- C: 3

- D: 4

- E:6

| w | х | у | z | r = f(w, x, y, z) |

|---|---|---|---|-------------------|

| 0 | 0 | 0 | 0 | 0                 |

| 0 | 0 | 0 | 1 | 1                 |

| 0 | 0 | 1 | 0 | ?                 |

| 0 | 0 | 1 | 1 | 1                 |

| 0 | 1 | 0 | 0 | 1                 |

| 0 | 1 | 0 | 1 | 1                 |

| 0 | 1 | 1 | 0 | 1                 |

| 0 | 1 | 1 | 1 | 0                 |

| 1 | 0 | 0 | 0 | 1                 |

| 1 | 0 | 0 | 1 | 1                 |

| 1 | 0 | 1 | 0 | 0                 |

| 1 | 0 | 1 | 1 | 1                 |

| 1 | 1 | 0 | 0 | 1                 |

| 1 | 1 | 0 | 1 | 1                 |

| 1 | 1 | 1 | 0 | 1                 |

| 1 | 1 | 1 | 1 | 0                 |

**Figure 2:** A truth table for the 4-input Boolean function f.

- b Using the Karnaugh map above (plus any subsequent optimisation steps you deem necessary), derive a Boolean expression for *f* that minimises the number of operators required. How many operators remain in said expression?

- A: 1

- B: 4

- C: 5

- D: 11

- E: 12

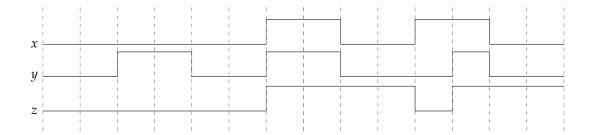

### **> Q44.** Consider the following waveform

which details the behaviour of three signals labelled x, y and z. Which of the following components *could* the behaviour illustrated relate to?

- A: an SR-type flip-flop

- B: an SR-type latch

- C: a D-type flip-flop

- D: a D-type latch

- E: a T-type flip-flop

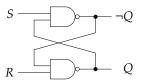

### $\triangleright$ **Q45.** The following diagram

illustrates a preliminary NAND-based SR-latch design, in the sense it currently lacks an enable signal. If Q and Q' denote the current and next state respectively, which of the following excitation tables

|     |   |   |   | Си     | rrent       | N                                      | ext       |

|-----|---|---|---|--------|-------------|----------------------------------------|-----------|

|     |   | S | R | Q      | $\neg Q$    | Q'                                     | $\neg Q'$ |

| 1   |   | 0 | 0 | 0      | 1           | 0                                      | 1         |

|     |   | 0 | 0 | 1<br>? | 0           | $\begin{vmatrix} 1 \\ 0 \end{vmatrix}$ | 0         |

| A { |   | 0 | 1 |        | ?           |                                        | 1         |

|     |   | 1 | 0 | ?      | 0<br>?<br>? | 1                                      | 0         |

| (   |   | 1 | 1 | ?      | ?           | 0                                      | 0         |

| 1   |   | 0 | 0 | ?      | ?           | 1                                      | 1         |

|     |   | 0 | 1 |        | ?<br>?<br>? | 1<br>1<br>0                            | 0         |

| в { |   | 1 | 0 | ?      |             |                                        | 1         |

|     |   | 1 | 1 | 0      | 1           | 0                                      | 1         |

| (   |   | 1 | 1 | 1      | 0           | 1                                      | 0         |

| _ [ | • | 0 | 0 | ?      | ?           | 0                                      | 1         |

| c { |   | 1 | 1 | ?      | ?           | 1                                      | 0         |

| _ } | K | 0 | ? | ?      | ?           | 0                                      | 1         |

| D { |   | 1 | ? | ?      | ?           | 1                                      | 0         |

| E { | ĸ | ? | 0 | ?      | ?           | 0                                      | 1         |

| r ( |   | ? | 1 | ?      | ?           | 1                                      | 0         |

correctly captures the behaviour of this circuit?

▷ Q46. Although perhaps unusual, the following diagram

illustrates a circuit with well defined behaviour. Based on analysis of this behaviour, which of the following components

A: a flip-flop

B: a latch

C: a RAM cell

D: a ROM cell

E: a clock multiplier

does the circuit implement?

$\triangleright$  **Q47.** A *m*-output, 1-bit demultiplexer connects a 1-bit input *x* to one of *m* separate 1-bit outputs (say  $r_i$  for  $0 \le i < m$ ). The output is selected using an *l*-bit control signal *c* (or, equivalently, *c* is a collection of *l* separate 1-bit control signals). If m = 5, what is the minimum value of *l* required?

A: 0

B: 1

C: 2

D: 3

E: 4

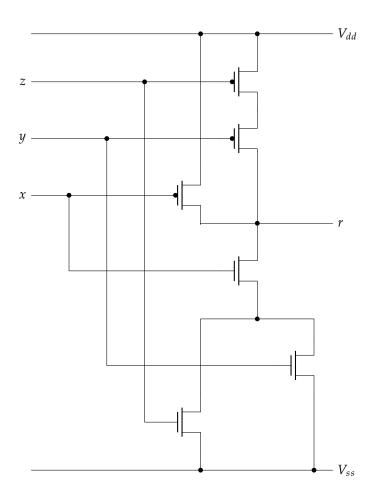

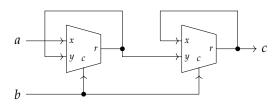

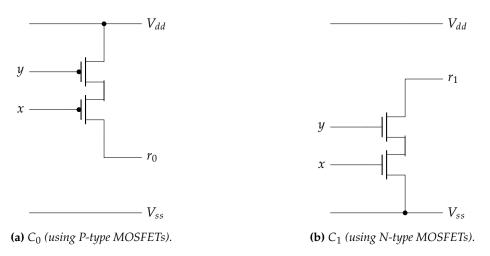

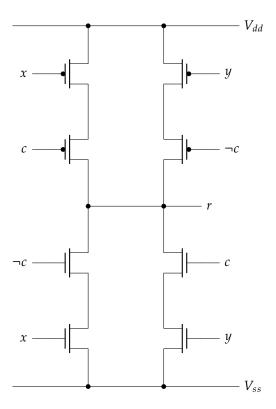

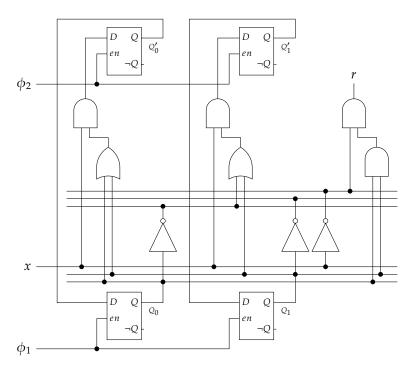

$\triangleright$  **Q48.** Figure 3 describes the implementation of two components denoted  $C_0$  and  $C_1$ . Each component  $C_i$  produces one output  $r_i$  given two inputs x and y, and has been implemented using MOSFET transistors.

**Figure 3:** *MOSFET-based implementations of*  $C_0$  *and*  $C_1$ .

a The truth table below includes 5 possibilities for outputs  $r_0$  and  $r_1$  (stemming from instances of  $C_0$  and  $C_1$ ), given x and y. Recall that  $V_{ss}$  and  $V_{dd}$  are used to represent 0 and 1 respectively: which option is correct?

|   |   | P     | ۸.    | E     | 3.      | (     | Ξ.    | Ι     | ).           | F     | Ξ.       |

|---|---|-------|-------|-------|---------|-------|-------|-------|--------------|-------|----------|

|   |   |       | Ì     |       | <u></u> |       | Ì     |       | Ć            |       | <u> </u> |

| x | y | $r_0$ | $r_1$ | $r_0$ | $r_1$   | $r_0$ | $r_1$ | $r_0$ | $r_1$        | $r_0$ | $r_1$    |

| 0 | 0 | 1     | 0     | 0     | 0       | 1     | 0     | Z     | 0            | 1     | Z        |

| 0 | 1 | 1     | 1     | 0     | 0       | 0     | 0     | Z     | Z            | Z     | Z        |

| 1 | 0 | 1     | 1     | 0     | 0       | 0     | 0     | Z     | $\mathbf{Z}$ | Z     | Z        |

| 1 | 1 | 0     | 1     | 1     | 0       | 0     | 0     | 1     | $\mathbf{Z}$ | Z     | 0        |

b The vendor of these components claims they can be used to implement any Boolean function; their reasoning is based on the fact that a NAND gate can be implemented using instances of  $C_0$  and  $C_1$ . Imagine you adhere to a design strategy where any given wire is driven by at most one non-**Z** value at any given time, and want to minimise the number of  $C_0$  and  $C_1$  instances used: how many of each do you need to implement a NAND gate?

| A     | ١.            | E     | 3.            |       | <b>.</b>      | Γ     | ).            | E     | Ξ.            |

|-------|---------------|-------|---------------|-------|---------------|-------|---------------|-------|---------------|

|       | $\overline{}$ |

| $C_0$ | $C_1$         |

| 1     | 1             | 5     | 3             | 3     | 5             | 3     | 3             | 5     | 5             |

- ▶ Q49. Moore's Law is an observation about the number of transistors which can be fabricated within some fixed unit of area: it observes that this number doubles roughly every two years. Which of the following properties of MOSFET-based transistors act as a constraint with respect to Moore's Law?

- A: Feature size

- **B:** Power consumption

- C: Heat dissipation

- D: All of the above

- E: None of the above

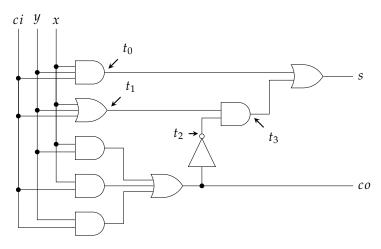

- $\triangleright$  **Q50.** Figure 4 shows an implementation of a full-adder cell. It uses three 1-bit inputs denoted x, y, and ci (the carry-in), to compute two 1-bit outputs denoted s (the sum) and co (the carry-out); several other intermediate wires, namely  $t_0$ ,  $t_1$ ,  $t_2$ , and  $t_3$ , are labelled for reference. Let

$$(x, y, ci) \rightarrow (x', y', ci')$$

denote a change in said inputs: the LHS captures current values, whereas the RHS captures next (or new) values. For example,

$$(0,0,0) \rightarrow (1,0,0)$$

toggles *x* from 0 to 1, while both *y* and *ci* remain 0. Which of the following options will cause *s* to toggle in the shortest period of time (i.e., with the shortest delay)?

**Figure 4:** An implementation of a full-adder cell.

A:  $(0,0,0) \rightarrow (0,0,1)$

B:  $(0,0,1) \rightarrow (0,1,1)$

C:  $(0,1,1) \rightarrow (0,0,1)$

$D: (1,1,1) \to (1,1,0)$

$E: (1,0,1) \to (0,1,1)$

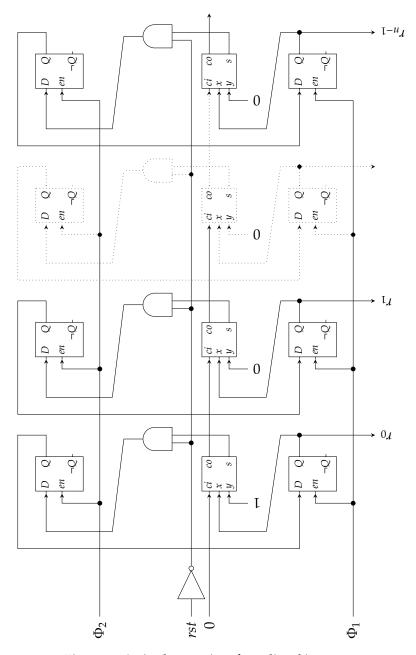

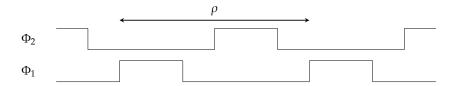

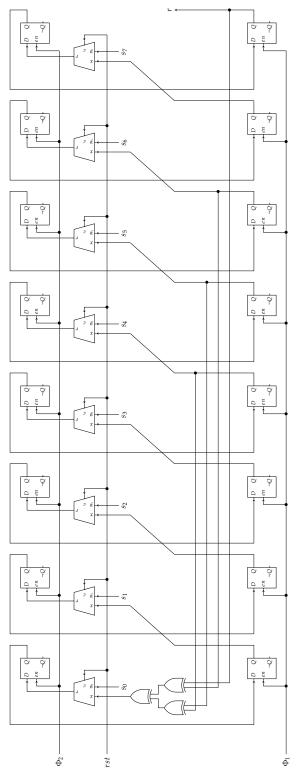

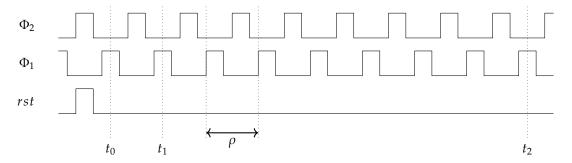

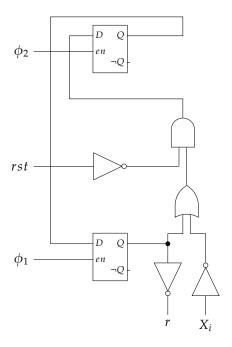

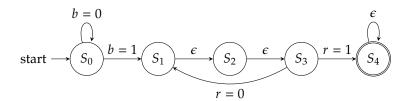

$\triangleright$  **Q51.** Figure 5 shows an implementation of a cyclic *n*-bit counter. While the counter is operational (i.e., while not reset, and given a clock signal), each  $r_i$  will transition between 0 and 1 at a different frequency. For the concrete case of n = 4, which does so at the lowest frequency?

$A: r_4$

B: *r*<sub>3</sub>

$C: r_2$

$D: r_1$

$E: r_0$

$\triangleright$  **Q52.** Consider a 16-bit register, constructed from CMOS-based D-type latches. Based on high-level reasoning about this component alone, if the initial value stored is  $DEAD_{(16)}$  then overwriting it with which of the following

A:  $BEEF_{(16)}$

B: F00D<sub>(16)</sub>

C: 1234<sub>(16)</sub>

D: FFFF<sub>(16)</sub>

$E: 0000_{(16)}$

might you expect to consume the most power?

▷ **Q53.** You are tasked with implementing the Boolean function

$$r = f(x, y, z) = (\neg x \land \neg y \land \neg z) \lor (y \land \neg z) \lor (y \land z).$$

Each of the five options (i.e., columns) in the table below

|          |   |              |   |              | E            |

|----------|---|--------------|---|--------------|--------------|

| 1.<br>2. | × | $\checkmark$ | × | ×            | $\checkmark$ |

| 2.       | × | ×            | × | ×            | $\checkmark$ |

| 3.       | × | ×            | X | $\checkmark$ | $\checkmark$ |

states whether f can (a tick) or cannot (a cross) be implemented using a given set of components (i.e., row), namely

**Figure 5:** *An implementation of a cyclic n-bit counter.*

- a an 8-input, 1-bit multiplexer,

- b a 4-input, 1-bit multiplexer,

- c a 2-input, 1-bit multiplexer, an OR gate, and a NOT gate,

plus the constant values 0 and 1. For example, option C states that f can be implemented by using component set 2 but not 1 or 3. Which option do you think is correct?

### **Decomposition Decomposition Decompositio**

i.e., that one can implement a NOT gate using one instance of a 2-input, 1-bit multiplexer component. Assuming you want to minimise the number of multiplexer instances, identify how many are required to implement the expression

$$(x \wedge y) \vee z$$

.

- A: 1

- B: 2

- C: 3

- D: 6

- E: 8

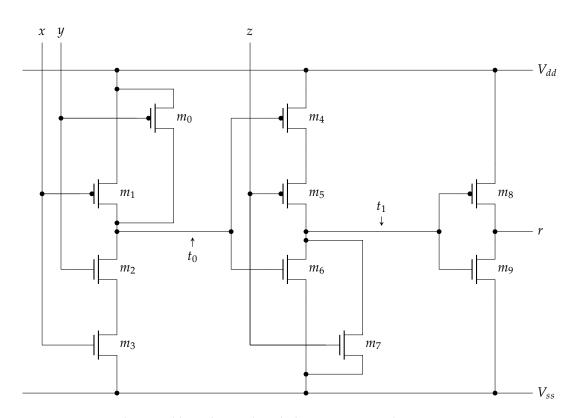

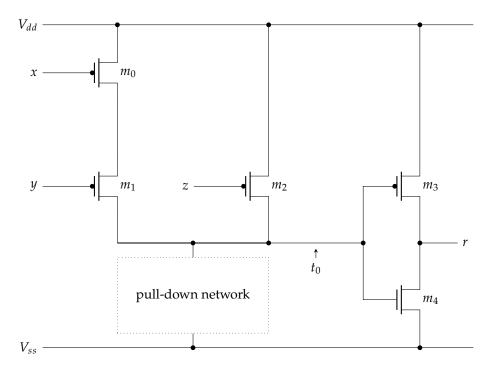

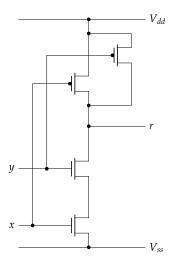

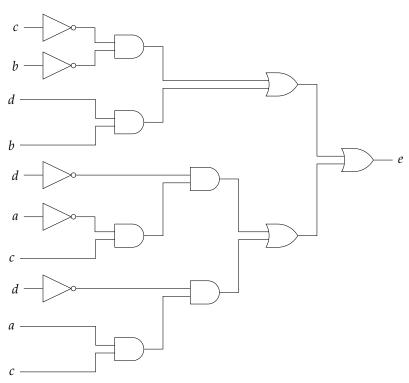

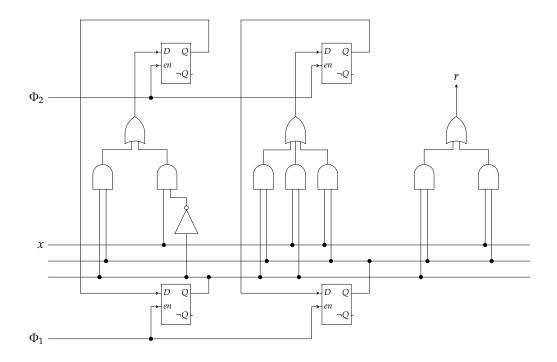

**Figure 6:** A combinatorial logic design, described using N-type and P-type MOSFET transistors.

$\triangleright$  **Q55.** Consider the combinatorial logic design as shown in Figure 6, which is described using N-type and P-type MOSFET transistors. Within the design, three inputs (i.e., x, y, and z) and one output (i.e., r) can be identified; note that several transistors (e.g.,  $m_0$ ) and intermediate signals (e.g.,  $t_0$ ) are annotated for reference. Which of the following Boolean expressions

A:  $\neg x$

B:  $\neg((x \ \overline{\lor} \ y) \ \overline{\land} \ z)$

C:  $(\neg(x \ \overline{\lor} \ y)) \ \overline{\land} \ z$

D:  $\neg(x \land y \land \neg z)$

**E:**  $\neg(x \lor y \lor \neg z)$

does the design implement?

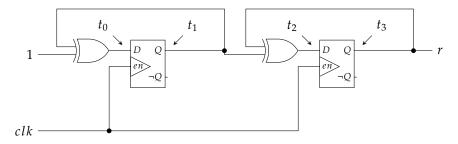

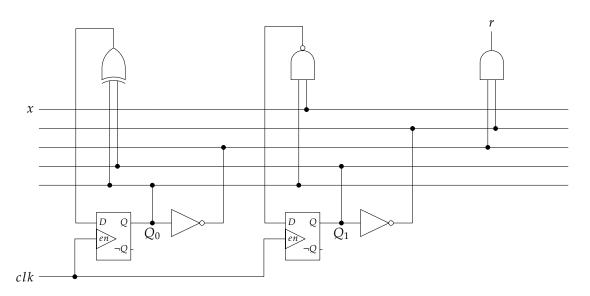

**Figure 7:** A sequential logic design, containing two D-type flip-flops.

$\triangleright$  **Q56.** Consider the sequential logic design as shown in Figure 7, which contains two D-type flip-flops. Within the design, one output (i.e., r) can be identified; note that several intermediate signals (e.g.,  $t_0$ ) are annotated for reference. If the clock signal clk has a frequency of 400MHz, what is the frequency of r?

A: 100MHz

B: 200MHz

C: 400MHz

D: 800MHz

E: 1600MHz

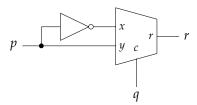

which is described using a 2-input, 1-bit multiplexer. Within the design, two inputs (i.e., p and q) and one output (i.e., r) can be identified. Which of the following Boolean expressions

A:  $r = \neg p$

B:  $r = p \wedge q$

C:  $r = \neg(p \land q)$

D:  $r = p \oplus q$

**E**:  $r = \neg(p \oplus q)$

correctly reflects the relationship between inputs and output?

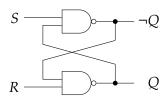

▷ Q58. A NAND-based SR latch implementation can be realised as follows: The following

**Figure 8:** A combinatorial logic design, described using N-type and P-type MOSFET transistors; note that the pull-down network is (partially) missing.

Imagine that the two NAND gates have a non-zero, but unequal gate delay associated with them, i.e., the top gate has the delay x whereas the bottom gate has the delay  $x \pm \delta$  for some x and  $\delta > 0$ . If the current input S = R = 0 is changed instantaneously to S = R = 1, what will the outputs be?

A:

$$Q = 1, \neg Q = 1$$

B: either

$$Q = 0$$

,  $\neg Q = 1$  or  $Q = 1$ ,  $\neg Q = 0$

C: either

$$Q = 1$$

,  $\neg Q = 1$  or  $Q = 0$ ,  $\neg Q = 0$

D:

$$Q = 0$$

,  $\neg Q = 0$

E: None of the above

$\triangleright$  **Q59.** Consider the combinatorial logic design as shown in Figure 8, which is described using N-type and P-type MOSFET transistors. Within the design, three inputs (i.e., x, y, and z) and one output (i.e., r) can be identified; note that several transistors (e.g.,  $m_0$ ) and intermediate signals (e.g.,  $t_0$ ) are annotated for reference. Despite the fact that the pull-down network is (partially) missing, it is still possible to infer how the design works: which of the following Boolean expressions

A:

$$r = x \oplus y$$

B:

$$r = (\neg x \land \neg y) \lor \neg z$$

C:

$$r = (\neg x \lor \neg y) \land \neg z$$

$$D: r = (x \wedge y) \vee z$$

$$E: r = (x \vee y) \wedge z$$

correctly reflects the relationship between inputs and output?

▶ **Q60.** Consider the following MOSFET transistor

If  $x \in \{0,1\}$  and  $en \in \{0,1\}$ , how many different values can r potentially take?

A: 1

B: 2

C: 3

D: 4

**E:** 5

⊳ **Q61.** Consider a combinatorial logic component defined by

$$r = f(x, y) = \begin{cases} 1 & x > y \\ 0 & \text{otherwise} \end{cases}$$

For how many combinations of the unsigned, 2-bit inputs x and y is the output r = 1?

A: 1

B: 2

C: 4

D: 6

E:8

Description Descr

Assuming that logic gates for NOT, AND, OR, and XOR require 1, 2, 2, and 4 units of area respectively, the general-purpose solution requires

$$32 \cdot (2 \cdot XOR + 2 \cdot AND + 1 \cdot OR) = 32 \cdot (2 \cdot 4 + 2 \cdot 2 + 1 \cdot 2) = 448$$

units of area due to the use of 32 full-adder cells. If the optimisation aims to minimise area, which of the following options

A: 2.00

B: 2.31

C: 2.33

D: 2.52

E: 3.14

most accurately reflects the improvement factor offered by the special-purpose solution?

$\triangleright$  **Q63.** Binary-Coded Decimal (BCD) is a representation for decimal integers, where each decimal digit in some x is represented independently by a 4-bit binary sequence in r. For example,

$$x = 123_{(10)} \mapsto \langle 0011_{(2)}, 0010_{(2)}, 0001_{(2)} \rangle = r.$$

Note that because each  $0 \le x_i < 10$  and  $2^4 = 16 > 10$ , some values of the associated BCD-encoded digit  $r_i$  are impossible.

Imagine you are asked to implement a 4-input Boolean function f using combinatorial logic, which will be used to process BCD-encoded digits. Select an option to complete blanks in the sentence "a Karnaugh map cell which contains a \_\_\_\_\_ can be treated as either \_\_\_\_ or \_\_\_ in order to \_\_\_\_\_ the resulting term", so that it correctly describes how you might deal with an impossible BCD-encoded digit.

A: don't care, AND, OR, eliminate

B: duplicate, 1, 0, verify

C: unknown, 1, 0, simplify

D: don't care, 1, 0, simplify

E: unknown, 0, 1, optimise

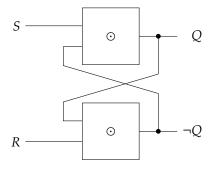

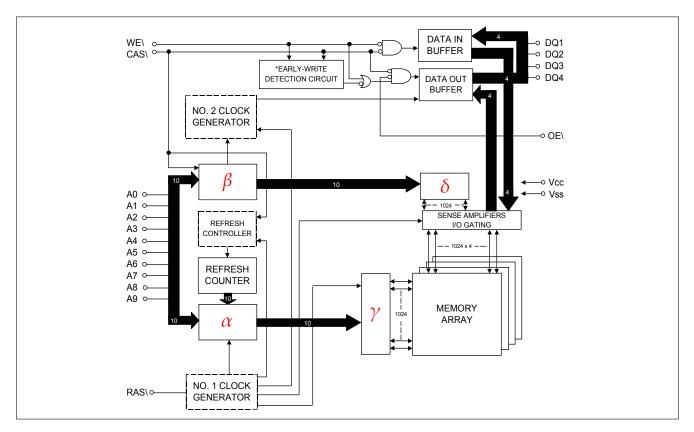

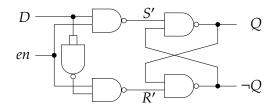

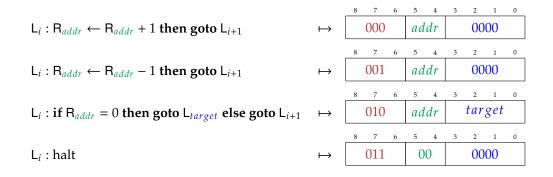

**Figure 9:** *An SR-latch, described in terms of placeholder components labelled* ⊙.

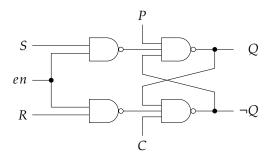

**Figure 10:** An SR-latch variant, which includes additional inputs P, C, and en.

Describes Q64. The block diagram in Figure 9, describes a sequential logic component, or, more specifically, an SR-type latch: it does so using two placeholder components labelled ⊙. If the associated excitation table is as follows

| S | R | Q | $\neg Q$ | Q' | $\neg Q'$ |

|---|---|---|----------|----|-----------|

| 1 | 1 | 0 | 1        | 0  | 1         |

| 1 | 1 | 1 | 0        | 1  | 0         |

| 1 | 0 | ? | ?        | 0  | 1         |

| 0 | 1 | ? | ?        | 1  | 0         |

| 0 | 0 | ? | ?        | ?  | ?         |

which of the following gate types

A: XOR

B: AND

C: OR

D: NAND

E: NOR

has been used to instantiate the placeholder components (i.e., replace each  $\odot$ )?

- $\triangleright$  **Q65.** Figure 10, describes a sequential logic component, or, more specifically, a variant of the SR-latch: in addition to *S* and *R*, it also includes the inputs labelled *P*, *C*, and *en*.

- a Which of the following options

|   | S and R      | P and C      |

|---|--------------|--------------|

| Α | synchronous  | synchronous  |

| В | synchronous  | asynchronous |

| C | asynchronous | synchronous  |

| D | asynchronous | asynchronous |

most accurately classifies the inputs?

b Which of the following options

|   | S and R     | P and C     |

|---|-------------|-------------|

| Α | active low  | active low  |

| В | active low  | active high |

| C | active high | active low  |

| D | active high | active high |

most accurately classifies the inputs?

ightharpoonup Abstractly, any functionality implemented using combinatorial logic can be viewed as an n-input, m-output Boolean function  $f:\{0,1\}^n \to \{0,1\}^m$ , i.e., a block

with n 1-bit input and m 1-bit output wires.

a Which of the following

A:

$$n = 4$$

,  $m = 1$

B:

$$n = 5$$

,  $m = 1$

C:

$$n = 16$$

,  $m = 4$

D:

$$n = 18$$

,  $m = 1$

E:

$$n = 18$$

,  $m = 4$

lists the correct values of *n* and *m* for a multiplexer that selects between four 4-bit values?

b Which of the following statements

A: For a half-adder

$$n = 2$$

,  $m = 1$ ; for a full-adder  $n = 4$ ,  $m = 2$

B: For a half-adder

$$n = 2$$

,  $m = 1$ ; for a full-adder  $n = 3$ ,  $m = 1$

C: For a half-adder

$$n = 2$$

,  $m = 2$ ; for a full-adder  $n = 3$ ,  $m = 2$

D: For a half-adder

$$n = 3$$

,  $m = 1$ ; for a full-adder  $n = 2$ ,  $m = 2$

E: For a half-adder

$$n = 3$$

,  $m = 2$ ; for a full-adder  $n = 2$ ,  $m = 2$

is correct?

- Classify each of the following statements as either true or false, then explain why using at most a few sentences.

- a Consider the following symbols

which, from left-to-right, describe a buffer, a NOT gate, an N-type MOSFET, and a P-type MOSFET respectively. One could argue the NOT gate  $(r = \neg x)$  is an "inverting version" of the buffer (r = x), a fact illustrated by an "inversion bubble" on the output; a similar argument could be made of the N-type MOSFET and the P-type MOSFET.

- b The organisation of N- and P-type MOSFET transistors shown in Figure 11 implements the Boolean expression  $r = (x \land \neg c) \lor (y \land c)$ , i.e., that reflecting a 2-input, 1-bit multiplexer.

- c Assuming m > 1, a combinatorial logic component with n inputs and m outputs can always be decomposed into m separate (potentially simpler) components.

**Figure 11:** A design that uses MOSFET-based transistors, with three inputs (labelled c, x, and y) and one output (labelled r).

- d Application of the Karnaugh map technique to a truth table describing a Boolean function  $f: \{0,1\}^n \to \{0,1\}^m$  will always yield the optimal implementation of said function.

- e A full-adder is functionally complete (or universal), in the sense that one can realise *all* standard Boolean operators (i.e., NOT, AND, and OR) and therefore *any* Boolean expression using instances of it alone.

- f A 4-input, 1-bit multiplexer can be implemented by using 13 or fewer standard logic gates (i.e., NOT gates, and 2-input AND and OR gates).

- ▷ **Q68.** Write the simplest (i.e., with **fewest** operators) possible Boolean expression that implements the Boolean function

$$r = f(x, y, z)$$

described by

|   | f | c |   |

|---|---|---|---|

| x | у | z | r |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | ? |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | ? |

| 1 | 1 | 1 | 1 |

where? denotes don't care.

ightarrow **Q69.** Take the Boolean expression

$$\neg(x \lor y)$$

and draw a gate-level circuit diagram that computes an equivalent resulting using only 2-input NAND gates.

$\triangleright$  **Q70.** Recall that an SR latch has two inputs *S* (or set) and *R* (or reset); if *S* = *R* = 1, the two outputs *Q* and ¬*Q* are undefined. This issue can be resolved by using a reset-dominate latch: the alternative design has the same inputs and outputs, but resets the latch (i.e., has *Q* = 0 and ¬*Q* = 1) whenever *S* = *R* = 1.

Using a gate-level **circuit diagram**, describe how a reset-dominate latch can be implemented using **only** NOR gates and at most **one** AND gate.

- ▷ Q71. The quality of the design for some hardware component is often judged by measuring efficiency, for example how quickly it can produce output on average. Name two other metrics that might be considered.

- Describe how *N*-type and *P*-type MOSFET transistors are constructed using silicon and how they operate

as switches.

- b Draw a diagram to show how *N*-type and *P*-type MOSFET transistors can be used to implement a NAND gate. Show your design works by describing the transistor states for each input combination.

- $\triangleright$  **Q73.** The following diagram

details a 2-input NAND gate comprised of two P-MOSFET transistors (top) and two N-MOSFET transistors (bottom). Draw a similar diagram for a 3-input NAND gate.

- $\triangleright$  **Q75.** Given that **?** is the don't care state, consider the following truth table which describes a function *p* with four inputs (*a*, *b*, *c* and *d*) and two outputs (*e* and *f*):

|                                 |   | 1                               | ŋ                               |                                                                         |                                                               |

|---------------------------------|---|---------------------------------|---------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------|

| а                               | b | С                               | d                               | е                                                                       | f                                                             |

| 0                               | 0 | 0                               | 0                               | 0                                                                       | 0                                                             |

| 0                               | 0 | 0                               | 1                               | 0                                                                       | 1                                                             |

| 0                               | 0 | 1                               | 0                               | 1                                                                       | 0                                                             |

| 0                               | 0 | 1                               | 1<br>0<br>1<br>0<br>1<br>0      | ?                                                                       | ?                                                             |

| 0                               | 1 | 0                               | 0                               | 0                                                                       | 1                                                             |

| 0                               | 1 | 0                               | 1                               | 1                                                                       | 0                                                             |

| 0                               | 1 | 1                               | 0                               | 0                                                                       | 0                                                             |

| 0<br>0<br>0<br>0<br>0<br>0<br>0 | 1 | 1<br>0<br>0<br>1<br>1<br>0<br>0 | 1                               | ?                                                                       | ?                                                             |

| 1                               | 0 | 0                               | 0                               | 1                                                                       | 0                                                             |

| 1 1                             | 0 | 0                               | 1                               | 0                                                                       | 0                                                             |

| 1                               | 0 | 1                               | 0                               | 0                                                                       | 1                                                             |

| 1                               | 0 | 1                               | 1                               | ?                                                                       | ?                                                             |

| 1                               | 1 | 1<br>1<br>0                     | 0                               | ?                                                                       | ?                                                             |

| 1                               | 1 | 0                               | 1<br>0<br>1<br>0<br>1<br>0<br>1 | 0<br>0<br>1<br>?<br>0<br>1<br>0<br>?<br>1<br>0<br>0<br>?<br>?<br>?<br>? | 0<br>1<br>0<br>?<br>1<br>0<br>0<br>?<br>0<br>0<br>1<br>?<br>? |

| 1                               | 1 | 1                               | 0                               | ?                                                                       | ?                                                             |

| 1                               | 1 | 1                               | 1                               | ?                                                                       | ?                                                             |

- a From the truth table above, write down the corresponding Sum of Products (SoP) equations for e and f.

- b Simplify the two SoP equations so that they use the minimum number of logic gates possible. You can assume the two equations can share logic.

- ▶ **Q76.** Using a Karnaugh map, derive a Boolean expression for the function

$$r = f(x, y, z)$$

described by the truth table

|                  |   | c |   |

|------------------|---|---|---|

|                  | J |   |   |

| $\boldsymbol{x}$ | y | z | r |

| 0                | 0 | 0 | 1 |

| 0                | 0 | 1 | 1 |

| 0                | 1 | 0 | 1 |

| 0                | 1 | 1 | 0 |

| 1                | 0 | 0 | 0 |

| 1                | 0 | 1 | 1 |

| 1                | 1 | 0 | 0 |

| 1                | 1 | 1 | ? |

where? denotes don't care.

- ▷ Q77. NAND is a universal logic gate in the sense that the behaviour of NOT, AND and OR gates can be implemented using only NAND. Show how this is possible using a truth table to demonstrate your solution.

- Described Descr

- ▶ **Q79.** Consider the following circuit where the propagation delay of logic gates in the circuit are 10ns for NOT, 20ns for AND, 20ns for OR and 60ns for XOR:

- a Draw a Karnaugh map for this circuit and derive a Sum of Products (SoP) expression for the result.

- b Describe advantages and disadvantages of your SoP expression and the dynamic behaviour it produces.

- c If the circuit is used as combinatorial logic within a clocked system, what is the maximum clock speed of the system?

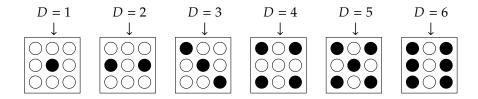

- $\triangleright$  **Q80.** A game uses nine LEDs to display the result of rolling a six-sided dice; the *i*-th LED, say  $L_i$  for 0 ≤ *i* < 9, is driven with 1 or 0 to turn it on or off respectively. A 3-bit register D represents the dice as an unsigned integer.

- a The LEDs are arranged as follows,

and the required mapping between dice and LEDs, given a filled dot means an LED is on, is

Using Karnaugh maps as appropriate, write a simplified Boolean expression for **each** LED (i.e., for **each**  $L_i$  in terms of D).

- b The 2-input XOR, AND, OR and NOT gates used to implement your expressions have propagation delays of 40, 20, 20 and 10 nanoseconds respectively. Calculate how many times per-second the dice can be rolled, i.e., *D* can be updated, if the LEDs are to provide the correct output.

- c The results of individual dice throws will be summed using a ripple-carry adder circuit, to give a total; each 3-bit output *D* will be added to and stored in an *n*-bit accumulator register *A*.

- i Using a high-level **block diagram**, show how an *n*-bit ripple-carry adder circuit is constructed from full-adder cells.

- ii If m = 8 throws of the dice are to be summed, what value for n should be selected?

- iii Imagine that instead of D, we want to add  $2 \cdot D$  to A. Doubling D can be achieved by computing either D + D or  $D \ll 1$  (i.e., a left-shift of D by 1 bit). Carefully state which method is preferable, and why.

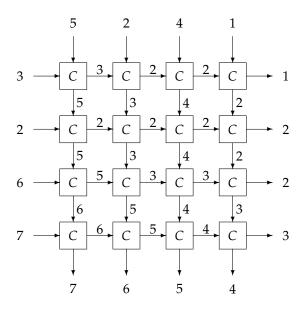

- $\triangleright$  **Q81.** Consider a simple component called *C* that compares two inputs *x* and *y* (both are unsigned 8-bit integers) in order to produce their maximum and minimum as two outputs:

Instances of *C* can be connected in a mesh to sort integers: the input is fed into the top and left-hand edges of the mesh, the sorted output appears on the bottom and right-hand edges. An example is given below:

- a Using standard building blocks (e.g., adder, multiplexer etc.) rather than individual logic gates, draw a **block diagram** that implements the component *C*.

- b Imagine that an  $n \times n$  mesh of components is created. Based on your design for C and clearly stating any **assumptions** you need to make, write down an expression for the critical path of such a mesh.

- c Algorithms for sorting integers can clearly be implemented on a general-purpose processor. Explain **two** advantages and **two** disadvantages of using such a processor versus using a mesh like that above.

- ▷ Q82. Imagine you are working for a company developing the "Pee", a portable games console. The user interface

is a fancy controller that has

- three fire buttons represented by the 1-bit inputs  $F_0$ ,  $F_1$  and  $F_2$ , and

- a 8-direction D-pad represented by the 3-bit input *D*

and you are charged with designing some aspects of it.

- a The fire button inputs are described as level triggered and active high; explain what this means (in comparison to the alternatives in each case).

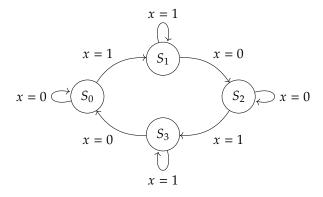

- b Some customers want an "autofire" feature that will automatically and repeatedly press the  $F_0$  fire button for them. The autofire can operate in four modes, selected by a switch called M: off (where the fire button  $F_0$  works as normal), slow, fast or very fast (where the fire button  $F_0$  is turned on and off repeatedly at the selected speed). Stating any assumptions and showing your working where appropriate, design a circuit that implements such a feature.

- c In an attempt to prevent counterfeiting, each controller can only be used with the console it was sold with. This protocol is used:

$$\begin{array}{ccc}

\varphi & C \\

c & \leftarrow \{0,1\}^3 \\

& \stackrel{c}{\longrightarrow} \\

r & = T(c)

\end{array}$$

which, in words, means that

- the console generates a random 3-bit number *c* and sends it to the controller,

- the controller computes a 3-bit result r = T(c) and sends it to the console,

- the console checks that r matches T(c) and assumes the controller is valid if so.

- i There is some debate as to whether the protocol should be synchronous or asynchronous; explain what your recommendation would be and why.

ii The function *T* is simply a look-up table. For example

$$T(x) = \begin{cases} 2 & \text{if } x = 0 \\ 6 & \text{if } x = 1 \\ 7 & \text{if } x = 2 \\ 1 & \text{if } x = 3 \end{cases} \qquad \begin{cases} 4 & \text{if } x = 4 \\ 0 & \text{if } x = 5 \\ 5 & \text{if } x = 6 \\ 3 & \text{if } x = 7 \end{cases}$$

Each pair of console and controller has such a *T* fixed inside them during the manufacturing process. Stating any assumptions and showing your working where appropriate, explain how **this** *T* might be implemented as a circuit.

- $\triangleright$  **Q83.** Imagine you have three Boolean values x, y, and z. Given access to **as many** AND and OR gates as you want but **only two** NOT gates, write a set of Boolean expressions to compute all three results ¬x, ¬y and ¬z.

- $\triangleright$  **Q84.** SAT is the problem of finding an assignment to n Boolean variables which means a given Boolean expression is satisfied, i.e., evaluates to 1. For example, given n=3 and the expression

$$(x \wedge y) \vee \neg z$$

,

x = 1, y = 1, z = 0 is one assignment (amongst several) which solves the associated SAT problem.

The ability to solve SAT can be used to test whether or not two n-input, 1-output combinatorial circuits  $C_1$  and  $C_2$  are equivalent. Show how this is possible.

$\triangleright$  **Q85.** Consider the following combinatorial circuit, which is the composition of four parts (labelled *A*, *B*, *C* and *REG*): each part is annotated with a name and an associated critical path. The circuit computes an output r = f(x) from the corresponding input x.

$$x \longrightarrow A$$

$$10ns \longrightarrow B$$

$$30ns \longrightarrow C$$

$$20ns \longrightarrow REG$$

$$10ns \longrightarrow r = f(x)$$

With respect to this circuit,

- a first define the terms latency and throughput, then

- b explain how and why you would expect use of pipelining to influence both metrics.

- ▶ **Q86.** The figure below shows a block of combinatorial logic built from seven parts; the name and latency of each part is displayed inside it. Note that the last part is a register which stores the result:

$$x \longrightarrow \begin{bmatrix} A \\ 40 \text{ns} \end{bmatrix} \longrightarrow \begin{bmatrix} B \\ 10 \text{ns} \end{bmatrix} \longrightarrow \begin{bmatrix} C \\ 30 \text{ns} \end{bmatrix} \longrightarrow \begin{bmatrix} D \\ 10 \text{ns} \end{bmatrix} \longrightarrow \begin{bmatrix} E \\ 50 \text{ns} \end{bmatrix} \longrightarrow \begin{bmatrix} F \\ 10 \text{ns} \end{bmatrix} \longrightarrow \begin{bmatrix} REG \\ 10 \text{ns} \end{bmatrix} \longrightarrow r = f(x)$$

It is proposed to pipeline the block of logic using two stages such that there is a pipeline register in between parts D and E:

$$x \longrightarrow \begin{matrix} A \\ 40 \text{ns} \end{matrix} \longrightarrow \begin{matrix} B \\ 10 \text{ns} \end{matrix} \longrightarrow \begin{matrix} C \\ 30 \text{ns} \end{matrix} \longrightarrow \begin{matrix} D \\ 10 \text{ns} \end{matrix} \longrightarrow \begin{matrix} REG \\ 10 \text{ns} \end{matrix} \longrightarrow \begin{matrix} E \\ 50 \text{ns} \end{matrix} \longrightarrow \begin{matrix} F \\ 10 \text{ns} \end{matrix} \longrightarrow \begin{matrix} REG \\ 10 \text{ns} \end{matrix} \longrightarrow r = f(x)$$

- a Explain the terms latency and throughput in relation to the idea of pipelining.

- b Calculate the overall latency and throughput of the initial circuit described above.

- c Calculate the overall latency and throughput of the circuit after the proposed change.

- d Calculate the number of extra pipeline registers required to maximise the circuit throughput; state this new throughput and the associated latency. Explain the advantages and disadvantages of this change.

# Part III: Basics of digital logic: minimisation via Karnaugh maps

This is a (large) set of example Boolean minimisation questions: each asks you to transform some truth table describing an *n*-input Boolean function into a Boolean expression. Each solution includes

- 1. a reference implementation (produced by forming a SoP expression with a full term for *each* minterm, i.e., row where r = 1), and

- 2. a Karnaugh map annotated with sensible groups, and an optimised implementation based on those groups.

The goal is to focus on producing the latter, since the former is somewhat easier. Keep in mind and take care wrt. the following:

- There are  $2^{2^n}$  Boolean functions with n inputs (or  $3^{2^n}$  if you include don't-care as a valid output); whereas for small n a complete set of functions is included, but for large n there is only a random sub-set.

- No real effort is made to order the questions, and only minor effort to avoid duplicates. That said, there should be no trivial (in the sense r = 1 or r = 0 for all inputs, e.g., tautological) cases.

- The questions and solutions are generated automatically, meaning a small but real chance of bugs in the associated implementation!

⊳ **Q87.**

| y | z | r |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

**> Q88.**

| у | Z | r |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

⊳ **Q89**.

| y | Z | r |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

⊳ **Q90**.

| у | Z | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

⊳ Q91.

| у | z | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

⊳ **Q92.**

| y | z | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

⊳ **Q93.**

| y | z | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

⊳ **Q94.**

| у | Z | r |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   |   |

⊳ **Q95.**

| y | z | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

⊳ **Q**96.

| y | z | r |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

⊳ **Q**97.

| у | Z | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | ? |

| 1 | 0 | ? |

| 1 | 1 | 1 |

⊳ **Q**98.

| у | Z | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | ? |

| 1 | 1 | 1 |

⊳ **Q99.**

| у | Z | r |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

**> Q100.**

| y | Z | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | ? |

⊳ Q101.

| х | у | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

⊳ Q102.

| x | у | z | r |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

⊳ Q103.

| х | у | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

⊳ Q104.

| х | у | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

|   |   |   |   |

⊳ Q105.

| х | y | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

⊳ Q106.

| х | y | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

⊳ Q107.

| x | у | z | r |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

⊳ Q108.

| x | Ŋ | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

⊳ Q109.

| $\boldsymbol{\chi}$ | у | z | r |

|---------------------|---|---|---|

| 0                   | 0 | 0 | 1 |

| 0                   | 0 | 1 | 0 |

| 0                   | 1 | 0 | 1 |

| 0                   | 1 | 1 | 0 |

| 1                   | 0 | 0 | 1 |

| 1                   | 0 | 1 | 1 |

| 1                   | 1 | 0 | 0 |

| 1                   | 1 | 1 | 1 |

|                     |   |   |   |

⊳ Q110.

| х | у | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

⊳ **Q111.**

| х | у | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

**> Q112.**

| x | у | z | r |

|---|---|---|---|

| 0 | 0 | 0 | ? |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | ? |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

⊳ **Q113.**

| х | y | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | ? |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | ? |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

⊳ Q114.

| х | у | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | ? |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | ? |

| 1 | 1 | 1 | 1 |

**> Q115.**

| y | z                          | r                                             |

|---|----------------------------|-----------------------------------------------|

| 0 | 0                          | 1                                             |

| 0 | 1                          | 0                                             |

| 1 | 0                          | 1                                             |

| 1 | 1                          | ?                                             |

| 0 | 0                          | ?                                             |

| 0 | 1                          | ?                                             |

| 1 | 0                          | 0                                             |

| 1 | 1                          | ?                                             |

|   | 0<br>0<br>1<br>1<br>0<br>0 | 0 0<br>0 1<br>1 0<br>1 1<br>0 0<br>0 1<br>1 0 |

⊳ **Q116.**

| х | у | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | ? |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | ? |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | ? |

**> Q117.**

| $\boldsymbol{x}$ | y | z | r |

|------------------|---|---|---|

| 0                | 0 | 0 | 1 |

| 0                | 0 | 1 | 0 |

| 0                | 1 | 0 | ? |

| 0                | 1 | 1 | 1 |

| 1                | 0 | 0 | 0 |

| 1                | 0 | 1 | 0 |

| 1                | 1 | 0 | 0 |

| 1                | 1 | 1 | ? |

⊳ Q118.

| x | у | z | r |

|---|---|---|---|

| 0 | 0 | 0 | ? |

| 0 | 0 | 1 | ? |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | ? |

| 1 | 1 | 1 | 0 |

⊳ Q119.

| х | у | Z | r |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | ? |

| 1 | 1 | 1 | ? |

⊳ Q120.

| x | у | z | r |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | ? |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | ? |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

**> Q121.**

| w                | х | y | Z      | r                                                                       |

|------------------|---|---|--------|-------------------------------------------------------------------------|

| 0                | 0 | 0 | 0      | 0                                                                       |

| 0                | 0 | 0 | 1      | 0                                                                       |

| 0                | 0 | 1 | 0      | 0                                                                       |

| 0<br>0<br>0      | 0 | 1 | 1      | 1                                                                       |

| 0                | 1 | 0 | 0      | 1                                                                       |

| 0                | 1 | 0 | 1      | 1                                                                       |

| 0                | 1 | 1 | 1<br>0 | 1                                                                       |

| 0                | 1 | 1 | 1      | 1                                                                       |

| 1                | 0 | 0 | 0      | 0                                                                       |

| 1<br>1<br>1<br>1 | 0 | 0 | 1      | 0                                                                       |

| 1                | 0 | 1 | 0      | 1                                                                       |

| 1                | 0 | 1 | 1      | 0                                                                       |

| 1                | 1 | 0 | 0      | 0                                                                       |

| 1                | 1 | 0 | 1      | 0<br>0<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0 |

| 1                | 1 | 1 | 0      |                                                                         |

| 1                | 1 | 1 | 1      | 1                                                                       |

⊳ Q122.

| w | $\boldsymbol{\chi}$ | y | z | r           |

|---|---------------------|---|---|-------------|

| 0 | 0                   | 0 | 0 | 1           |

| 0 | 0                   | 0 | 1 | 0           |

| 0 | 0                   | 1 | 0 | 0           |

| 0 | 0                   | 1 | 1 | 1           |

| 0 | 1                   | 0 | 0 | 1           |

| 0 | 1                   | 0 | 1 | 1           |

| 0 | 1                   | 1 | 0 | 1           |

| 0 | 1                   | 1 | 1 | 1 0         |

| 1 | 0                   | 0 | 0 |             |

| 1 | 0                   | 0 | 1 | 1<br>1      |

| 1 | 0                   | 1 | 0 | 0           |

| 1 | 0                   | 1 | 1 | 0           |

| 1 | 1                   | 0 | 0 |             |

| 1 | 1                   | 0 | 1 | 1<br>0<br>0 |

| 1 | 1                   | 1 | 0 | 0           |

| 1 | 1                   | 1 | 1 | 0           |

⊳ Q123.

| w | x | y | z | r                                    |

|---|---|---|---|--------------------------------------|

| 0 | 0 | 0 | 0 | 0                                    |

| 0 | 0 | 0 | 1 | 1                                    |

|   | 0 | 1 | 0 | 0                                    |

| 0 | 0 | 1 | 1 | 1<br>0<br>0<br>0                     |

| 0 | 1 | 0 | 0 | 0                                    |

| 0 | 1 | 0 | 1 | 1                                    |

| 0 | 1 | 1 | 0 | 1                                    |

| 0 | 1 | 1 | 1 | 0                                    |

| 1 | 0 | 0 | 0 | 1                                    |

| 1 | 0 | 0 | 1 | 0                                    |

| 1 | 0 | 1 | 0 | 0                                    |

| 1 | 0 | 1 | 1 | 1<br>1<br>0<br>1<br>0<br>0<br>1<br>0 |

| 1 | 1 | 0 | 0 | 0                                    |

| 1 | 1 | 0 | 1 | 0                                    |

| 1 | 1 | 1 | 0 | 1 0                                  |

| 1 | 1 | 1 | 1 | 0                                    |

⊳ Q124.

| w                          | х | у | Z   | r                                                             |

|----------------------------|---|---|-----|---------------------------------------------------------------|

| 0                          | 0 | 0 | 0   | 0                                                             |

| 0                          | 0 | 0 | 1   | 0                                                             |

| 0                          | 0 | 1 | 0   | 0                                                             |

| 0                          | 0 | 1 | 1 0 | 1                                                             |

| 0                          | 1 | 0 | 0   | 1                                                             |

| 0<br>0<br>0<br>0<br>0<br>0 | 1 | 0 | 1   | 1                                                             |

| 0                          | 1 | 1 | 1   | 1                                                             |

| 0                          | 1 | 1 | 1   | 1                                                             |

| 1                          | 0 | 0 | 0   | 1                                                             |

| 1                          | 0 | 0 | 1   | 1                                                             |

| 1                          | 0 | 1 | 1 0 | 1                                                             |

| 1                          | 0 | 1 | 1   | 1                                                             |

| 1                          | 1 | 0 | 0   | 1                                                             |

| 1                          | 1 | 0 | 1   | 0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

| 1                          | 1 | 1 | 0   | 1                                                             |

| 1                          | 1 | 1 | 1   | 0                                                             |

⊳ Q125.

| w | х      | у | Z      | r                                         |

|---|--------|---|--------|-------------------------------------------|

| 0 | 0      | 0 | 0      | 1                                         |

| 0 | 0      | 0 | 1      | 1                                         |

| 0 | 0      | 1 | 1<br>0 | 1                                         |

| 0 | 0      | 1 | 1      | 1<br>1<br>0                               |

| 0 | 1      | 0 | 1 0    | 1                                         |

| 0 | 1      | 0 | 1      | 1<br>0                                    |

| 0 | 1      | 1 | 0      | 1                                         |

| 0 | 1      | 1 |        | 1                                         |

| 1 | 1<br>0 | 1 | 1 0    | 1                                         |

| 1 | 0      | 0 | 1      | 1                                         |

| 1 | 0      | 1 | 0      | 0                                         |

| 1 | 0      | 1 | 1      | 0                                         |

| 1 | 1      | 0 | 0      | 1                                         |

| 1 | 1      | 0 |        | 1<br>1<br>1<br>1<br>0<br>0<br>1<br>0<br>0 |

| 1 | 1      | 1 | 1<br>0 | 0                                         |

| 1 | 1      | 1 | 1      | 1                                         |

⊳ Q126.

| w | $\boldsymbol{x}$ | y | z | r                               |

|---|------------------|---|---|---------------------------------|

| 0 | 0                | 0 | 0 | 1                               |

| 0 | 0                | 0 | 1 | 0                               |

|   | 0                | 1 | 0 | 0                               |

| 0 | 0                | 1 | 1 | 0                               |

| 0 | 1                | 0 | 0 | 1                               |

| 0 | 1                | 0 | 1 | 0                               |

| 0 | 1                | 1 | Ω | 0                               |

| 0 | 1                | 1 | 1 | 1                               |

| 1 | 0                | 0 | 0 | 0                               |

| 1 | 0                | 0 | 1 | 1                               |

| 1 | 0                | 1 | 0 | 0                               |

| 1 | 0                | 1 | 1 | 0<br>1<br>0<br>1<br>0<br>0<br>0 |

| 1 | 1                | 0 | 0 | 0                               |

| 1 | 1                | 0 | 1 | 1<br>1                          |

| 1 | 1                | 1 | 0 | 1                               |

| 1 | 1                | 1 | 1 | 1                               |

⊳ **Q127.**

| w                          | х | у | Z | r                                                                  |

|----------------------------|---|---|---|--------------------------------------------------------------------|

| 0                          | 0 | 0 | 0 | 0                                                                  |