### Computer Architecture

### Daniel Page

Department of Computer Science, University Of Bristol, Merchant Venturers Building, Woodland Road, Bristol, BS8 1UB. UK. ⟨csdsp@bristol.ac.uk⟩

September 5, 2025

Keep in mind there are *two* PDFs available (of which this is the latter):

- 1. a PDF of examinable material used as lecture slides, and

- 2. a PDF of non-examinable, extra material:

- the associated notes page may be pre-populated with extra, written explaination of material covered in lecture(s), plus

anything with a "grey'ed out" header/footer represents extra material which is

- useful and/or interesting but out of scope (and hence not covered).

| Notes. |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

| 1      |  |  |

|        |  |  |

|        |  |  |

| 1      |  |  |

|        |  |  |

|        |  |  |

| 1      |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

| Notes: |  |  |

### COMS10015 lecture: week #4

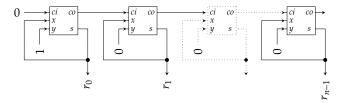

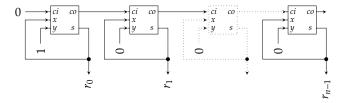

▶ Problem: design a cyclic *n*-bit **counter**, i.e., a component whose output *r* steps through values

$$0,1,\ldots,2^n-1,0,1,\ldots$$

but is otherwise uncontrolled (or "free running").

| © Daniel Page (csdsp@bristol.ac.uk) |  |

|-------------------------------------|--|

| Computer Architecture               |  |

git # b282dbb9 @ 2025-09-0

### COMS10015 lecture: week #4

▶ Problem: design a cyclic *n*-bit **counter**, i.e., a component whose output *r* steps through values

$$0, 1, \ldots, 2^n - 1, 0, 1, \ldots$$

but is otherwise uncontrolled (or "free running").

$\blacktriangleright$  (Potential) solution: we already have an *n*-bit adder that can compute x + y, i.e.,

### COMS10015 lecture: week #4

▶ Problem: design a cyclic *n*-bit **counter**, i.e., a component whose output *r* steps through values

$$0, 1, \ldots, 2^n - 1, 0, 1, \ldots$$

but is otherwise uncontrolled (or "free running").

ightharpoonup (Potential) solution: we already have an n-bit adder that can compute x + y, i.e.,

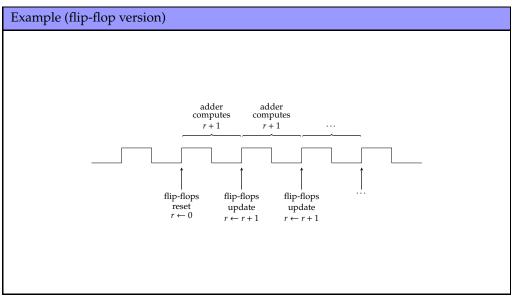

so we'll just have it compute  $r \leftarrow r + 1$  over and over again.

© Daniel Page (csdsp@bristol.ac.uk)

Computer Architecture

git # b282dbb9 @ 2025-09-0

#### COMS10015 lecture: week #4

▶ Problem: design a cyclic *n*-bit **counter**, i.e., a component whose output *r* steps through values

$$0,1,\ldots,2^n-1,0,1,\ldots$$

but is otherwise uncontrolled (or "free running").

$\triangleright$  (Potential) solution: we already have an *n*-bit adder that can compute x + y, i.e.,

so we'll just have it compute  $r \leftarrow r + 1$  over and over again;

- ▶ (New) problem: this won't work, because, for example,

- 1. we can't initialise the value, and

- 2. we don't let the output of each full-adder settle before it's used again as an input.

| Notes: |

|--------|

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

#### COMS10015 lecture: week #4

- (Actual) problem: combinatorial logic has some limitations, namely we can't

- control *when* a design computes some output (it does so continuously), nor

- remember the output when produced.

- ▶ (Actual) solution, and so agenda: sequential logic design, where, crucially,

- the output is a function of the input plus any state (e.g., stemming from previous inputs),

- computation is viewed as being discrete, i.e., step-by-step,

### via coverage of

- synchronisation of components clocks

- components that maintain state latches, flip-flops, and registers

- mechanism for computational steps structure plus strategy

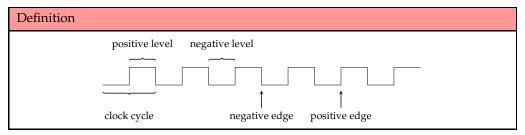

### Part 1: clocks (1)

▶ Concept: a **clock** is a signal that oscillates (or alternates) between 1 and 0.

#### where

- the clock signal is typically either

- an input which needs to be supplied externally, or

produced internally by a clock generator.

- we use features of the clock to

- 1. trigger events (e.g., steps in some sequence of computations), and/or

- 2. synchronise components.

- the clock frequency is how many clock cycles happen per-second; it must be

- fast enough to to satisfy the design goals, yet

- slow enough to cope with the critical path of a given step.

| Notes: |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

| Notes: |  |  |

|        |  |  |

|        |  |  |

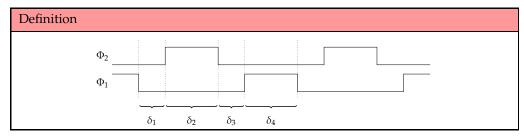

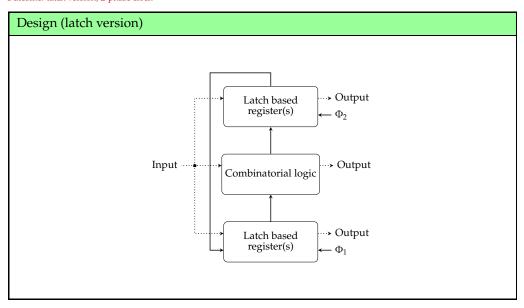

### Part 1: clocks (2)

**C**oncept: an *n*-phase clock is distributed as *n* separate signals along *n* separate wires.

where for n = 2, for example,

- features in a 1-phase clock (e.g., cycle, levels and edges), generalise to  $\Phi_1$  and  $\Phi_2$ ,

- there is a guarantee that positive levels of  $\Phi_1$  and  $\Phi_2$  don't overlap, and

- the behaviour is parameterisable by altering  $\delta_i$ .

© Daniel Page (csdsp@bristol.ac.uk)

Computer Architecture

git # b282dbb9 @ 2025-09-03

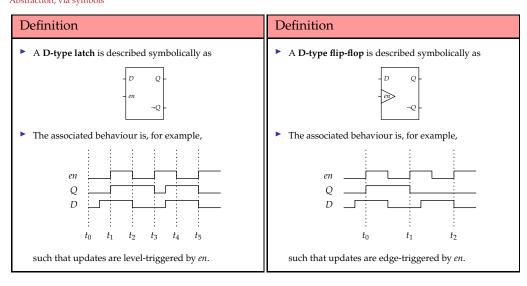

Part 2: latches, flip-flops, and register (1) Concepts

### Definition

A bistable component can exist in two stable states, i.e., 0 or 1: at a given point, it can

- retain some **current state** *Q* (which can also be read as an output), *and*

- ightharpoonup be updated to some **next state** Q' (which is provided as an input)

under control of an enable signal en.

#### Definition

The behaviour of a bistable is described by an **excitation table**, and sometimes expressed using a **characteristic equation**: versus, e.g., a truth table, the idea is to capture the notion of time (cf. current and next).

### Definition

A given bistable component controlled by an enable signal en can be

- 1. level-triggered, i.e., updated by a given level on en, or

- 2. **edge-triggered**, i.e., updated by a given edge on *en*.

The former type is termed a **latch**, whereas the latter type is termed a **flip-flop**.

| Notes: |  |

|--------|--|

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

| Notes: |  |

### Part 2: latches, flip-flops, and register (2)

### Definition

An "SR" latch/flip-flop component has two inputs S (or set) and R (or reset):

- when enabled, if

- ightharpoonup S = 0 and R = 0, the component retains Q,

- S = 1 and R = 0, the component updates to Q = 1, S = 0 and R = 1, the component updates to Q = 0,

- S = 1 and R = 1, the component is meta-stable

but

when not enabled, the component is in storage mode

The behaviour of such a component is specified by

$$Q' = S \vee (\neg R \wedge Q),$$

and/or

|   |   | Current |          | N  | ext       |

|---|---|---------|----------|----|-----------|

| S | R | Q       | $\neg Q$ | Q' | $\neg Q'$ |

| 0 | 0 | 0       | 1        | 0  | 1         |

| 0 | 0 | 1       | 0        | 1  | 0         |

| 0 | 1 | ?       | ?        | 0  | 1         |

| 1 | 0 | ?       | ?        | 1  | 0         |

| 1 | 1 | ?       | ?        | ?  | ?         |

### Definition

A "D" latch/flip-flop component has one input *D*:

- when enabled, if

- $\triangleright$  D = 1, the component updates to Q = 1,

- D = 0, the component updates to Q = 0,

when not enabled, the component is in storage mode

The behaviour of such a component is specified by

$$Q' = D$$

,

and/or

|   | Cu | rrent    | N  | ext       |

|---|----|----------|----|-----------|

| D | Q  | $\neg Q$ | Q' | $\neg Q'$ |

| 0 | ?  | ?        | 0  | 1         |

| 1 | ?  | ?        | 1  | 0         |

### Part 2: latches, flip-flops, and register (3) Concepts

### Definition

A "JK" latch/flip-flop component has two inputs J (or set) and *K* (or **reset**):

- when enabled, if

- ▶ J = 0 and K = 0, the component retains Q,

- J = 1 and K = 0, the component updates to Q = 1,

- J = 0 and K = 1, the component updates to  $\widetilde{Q} = 0$ ,

- I = 1 and K = 1, the component toggles Q,

when not enabled, the component is in storage mode so retains Q.

The behaviour of such a component is specified by

$$Q' = (I \land \neg Q) \lor (\neg K \land Q),$$

and/or

|   |   | Current |          | N  | ext       |

|---|---|---------|----------|----|-----------|

| J | K | Q       | $\neg Q$ | Q' | $\neg Q'$ |

| 0 | 0 | 0       | 1        | 0  | 1         |

| 0 | 0 | 1       | 0        | 1  | 0         |

| 0 | 1 | ?       | ?        | 0  | 1         |

| 1 | 0 | ?       | ?        | 1  | 0         |

| 1 | 1 | 0       | 1        | 1  | 0         |

| 1 | 1 | 1       | 0        | 0  | 1         |

### Definition

A "T" latch/flip-flop component has one input T:

- when enabled, if

- T = 0, the component retains Q,

- T = 1, the component toggles  $\widetilde{Q}$ ,

when not enabled, the component is in storage mode so retains Q.

The behaviour of such a component is specified by

$$Q' = (T \land \neg Q) \lor (\neg T \land Q) = T \oplus Q,$$

and/or

|   | Current |          | N  | ext       |

|---|---------|----------|----|-----------|

| T | Q       | $\neg Q$ | Q' | $\neg Q'$ |

| 0 | 0       | 1        | 0  | 1         |

| 0 | 1       | 0        | 1  | 0         |

| 1 | 0       | 1        | 1  | 0         |

| 1 | 1       | 0        | 0  | 1         |

| Notes. |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

| Notes: |  |  |

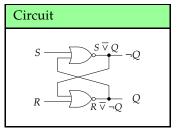

## Part 2: latches, flip-flops, and register (4) Design(s)

- ▶ Problem #1: we need an initial design for, e.g., an SR latch.

- ► Solution: use two *cross-coupled* NOR gates.

© Daniel Page (csdsp@bristol.ac.uk)

Computer Architecture

University of BRISTOL

git # b282dbb9 @ 2025-09-0

# Part 2: latches, flip-flops, and register (4) Design(s)

- ▶ Problem #1: we need an initial design for, e.g., an SR latch.

- ► Solution: use two *cross-coupled* NOR gates.

| Circuit                                                                                   | Example ( $S = 1, R = 0, \checkmark$ )                                                                                       | Example ( $S = 0, R = 1, \checkmark$ )               |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| $S \xrightarrow{S \overline{\vee} Q} \neg Q$ $R \xrightarrow{R \overline{\vee} \neg Q} Q$ | $\begin{array}{c c} S & \xrightarrow{1} & \xrightarrow{0} & \neg Q \\ R & \xrightarrow{0} & \xrightarrow{1} & Q \end{array}$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| Example ( $S = 1, R = 1, \times$ )                                                        | Example ( $S = 0, R = 0, \sqrt{)}$                                                                                           | Example $(S = 0, R = 0, \checkmark)$                 |

|                                                                                           |                                                                                                                              |                                                      |

| Notes: |  |

|--------|--|

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

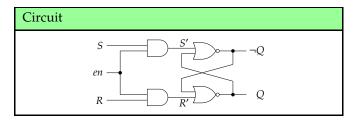

### Part 2: latches, flip-flops, and register (5) Design(s)

- ▶ Problem #2: we'd like to control when updates occur.

- ► Solution: *gate S* and *R*, i.e.,

### noting that

- ightharpoonup the same internal latch is evident, now with inputs S' and R',

- the external latch is such that

$$en = 0$$

$\Rightarrow$   $S' = S \land en = S \land 0 = 0$

$\Rightarrow$   $R' = R \land en = R \land 0 = 0$

$en = 1$   $\Rightarrow$   $S' = S \land en = S \land 1 = S$

$\Rightarrow$   $R' = R \land en = R \land 1 = R$

University of BRISTOL

git # b282dbb9 @ 2025-09-0

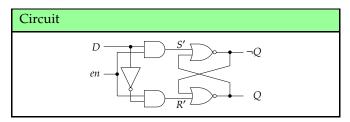

# Part 2: latches, flip-flops, and register (6) Design(s)

- ▶ Problem #3: we'd like to avoid the issue of meta-stability.

- ▶ Solution: force  $R = \neg S$  so we get either S = 0 and R = 1, or S = 1 and R = 0.

### Part 2: latches, flip-flops, and register (7)

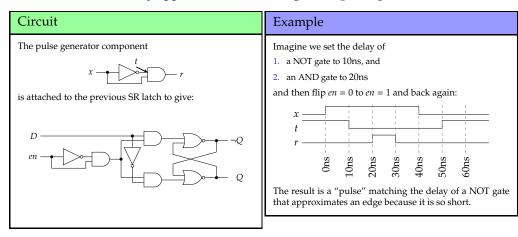

- ▶ Problem #4: we'd like an edge-triggered, rather than level-triggered design.

- ▶ Solution #1: "cheat" by approximation of an edge via a pulse generator.

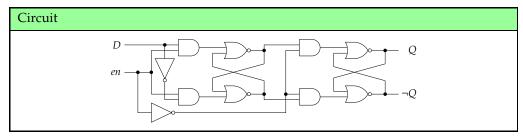

▶ Problem #4: we'd like an edge-triggered, rather than level-triggered design.

▶ Solution #2: adopt a primary-secondary organisation of *two* latches, i.e.,

where the idea is to split a clock cycle into to half-cycles:

primary latch is enabled secondary latch is enabled

### meaning

Design(s)

- while en = 1, i.e., positive level on en, primary latch stores input, and

when en = 0, i.e., negative edge on en, secondary latch stores output of primary latch, and hence we get edge-triggered behaviour.

Notes:

· Historically, the terms master and slave have often been used in place of primary and secondary. Per [8, Section 1.1], however, and despite some debate, the former are typically viewed as inappropriate now. We deliberately use the latter, therefore, noting that doing so may imply a need to translate the former when aligning with other literature.

## Part 2: latches, flip-flops, and register (9) Abstraction, via symbols

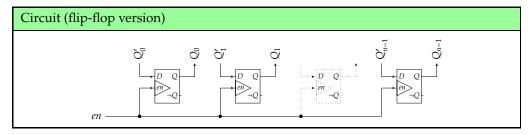

Part 2: latches, flip-flops, and register (10) Aggregation, via registers

▶ Concept: we typically combine latches (resp. flip-flops) into registers, i.e.,

- there are *n* instances, so we can store an *n*-bit value: the *i*-th instance stores the *i*-th bit,

- access is conceptually straightforward:

read from register : use current value Q write to register : drive next value onto Q', then trigger update via en

all instance share same *en*, so access to them is synchronised.

| Notes: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

## Part 2: latches, flip-flops, and register (10) Aggregation, via registers

▶ Concept: we typically combine latches (resp. flip-flops) into **registers**, i.e.,

### where

- there are *n* instances, so we can store an *n*-bit value: the *i*-th instance stores the *i*-th bit,

- ► access is conceptually straightforward:

read from register : use current value Q

write to register: drive next value onto Q', then trigger update via en

▶ all instance share same *en*, so access to them is synchronised.

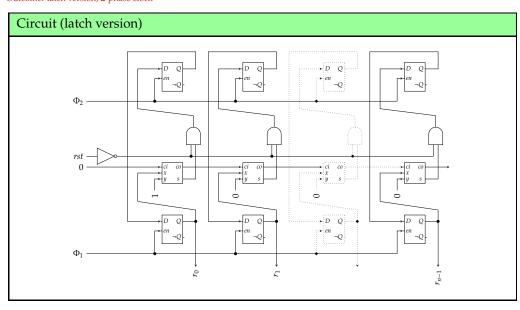

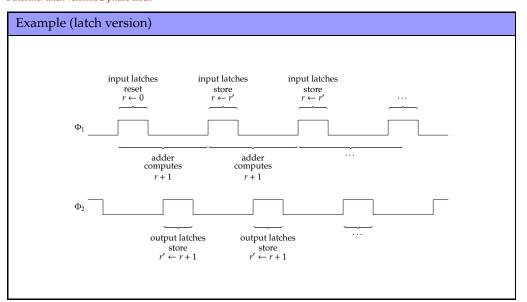

Part 3: structure plus strategy (1) Outcome: latch version, 2-phase clock

Part 3: structure plus strategy (2) Outcome: latch version, 2-phase clock

Part 3: structure plus strategy (3) Outcome: latch version, 2-phase clock

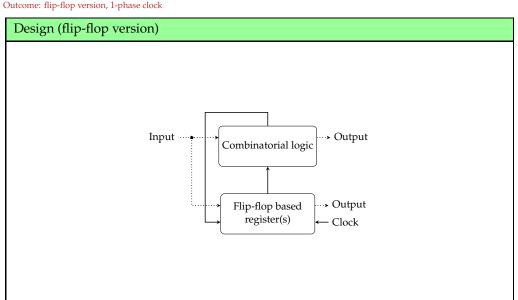

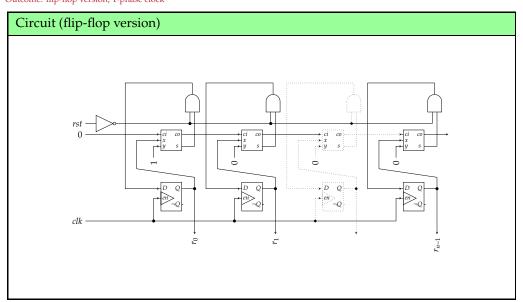

Part 3: structure plus strategy (4) Outcome: flip-flop version, 1-phase clock

Part 3: structure plus strategy (5) Outcome: flip-flop version, 1-phase clock

## Part 3: structure plus strategy (6) Outcome: flip-flop version, 1-phase clock

### Conclusions

### ► Take away points:

- 1. Sequential logic design is typically hard(er) to understand (at first) than combinatorial logic design: invest some effort to address this now!

- 2. The main concept and challenge is *time*:

- this goes beyond time in the sense of delay,

the goal is step-by-step, controlled (versus continuous, uncontrolled) computation,

we need to understand and manage, e.g., with parallelism and synchronisation.

| Notes: |  |

|--------|--|

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

| Notes: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

### Conclusions

| Tal | ke | av | vav | po | ints: |

|-----|----|----|-----|----|-------|

|     |    |    |     |    |       |

- 3. There is at least one higher-level design principle evident: we often see

- a data-path, of computational and/or storage components, and

- a control-path, that tells components in the data-path what to do and when to do it,

although the counter control-path is (very) simple.

4. The next step is to formalise this, allowing solution of more complex problems, e.g., through more complex forms of control.

© Daniel Page (csdsp@bristol.ac.uk) Computer Architecture

git # b282dbb9 @ 2025-09-0

### Additional Reading

- ▶ Wikipedia: Sequential logic. URL: https://en.wikipedia.org/wiki/Sequential\_logic.

- D. Page. "Chapter 2: Basics of digital logic". In: A Practical Introduction to Computer Architecture. 1st ed. Springer, 2009.

- W. Stallings. "Chapter 11: Digital logic". In: Computer Organisation and Architecture. 9th ed. Prentice Hall, 2013.

- A.S. Tanenbaum and T. Austin. "Section 3.2.2: Clocks". In: Structured Computer Organisation. 6th ed. Prentice Hall, 2012.

- A.S. Tanenbaum and T. Austin. "Section 3.3.4: Latches". In: Structured Computer Organisation. 6th ed. Prentice Hall, 2012.

- A.S. Tanenbaum and T. Austin. "Section 3.3.4: Flip-flops". In: Structured Computer Organisation. 6th ed. Prentice Hall, 2012.

- A.S. Tanenbaum and T. Austin. "Section 3.3.4: Registers". In: Structured Computer Organisation. 6th ed. Prentice Hall, 2012.

| Notes: |  |

|--------|--|

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

| Notes: |  |

| Totes. |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

### References

- Wikipedia: Sequential logic. URL: https://en.wikipedia.org/wiki/Sequential\_logic (see p. 59). [1]

- D. Page. "Chapter 2: Basics of digital logic". In: A Practical Introduction to Computer Architecture. 1st ed. Springer, 2009 (see p. 59).

- W. Stallings. "Chapter 11: Digital logic". In: Computer Organisation and Architecture. 9th ed. Prentice Hall, 2013 (see p. 59).

- A.S. Tanenbaum and T. Austin. "Section 3.2.2: Clocks". In: Structured Computer Organisation. 6th ed. Prentice Hall, 2012 (see

- A.S. Tanenbaum and T. Austin. "Section 3.3.4: Flip-flops". In: Structured Computer Organisation. 6th ed. Prentice Hall, 2012 (see [5] p. <del>59</del>).

- A.S. Tanenbaum and T. Austin. "Section 3.3.4: Latches". In: Structured Computer Organisation. 6th ed. Prentice Hall, 2012 (see [6]

- [7]

- [8]

| <br>© Daniel Page ( saspābristol.ac.u)<br>Computer Architecture                           | University of<br>BRISTOL                 | git#b282dbb9@2025-09-03                        |

|-------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------|

|                                                                                           |                                          |                                                |

|                                                                                           |                                          |                                                |

|                                                                                           |                                          |                                                |

|                                                                                           |                                          |                                                |

| M. Knodel and N. ten Oever. <i>Terminology</i> , Draft. 2018. URL: https://tools.ietf.org |                                          |                                                |

| A.S. Tanenbaum and T. Austin. "Section 3. p. 59).                                         | 3.4: Registers". In: Structured Computer | Organisation. 6th ed. Prentice Hall, 2012 (see |

| P. 37).                                                                                   |                                          |                                                |

| Notes: |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |