# Computer Architecture

# Daniel Page

Department of Computer Science, University Of Bristol, Merchant Venturers Building, Woodland Road, Bristol, BS8 1UB. UK. ⟨csdsp@bristol.ac.uk⟩

September 5, 2025

Keep in mind there are *two* PDFs available (of which this is the latter):

- 1. a PDF of examinable material used as lecture slides, and

- 2. a PDF of non-examinable, extra material:

- the associated notes page may be pre-populated with extra, written explaination of material covered in lecture(s), plus

anything with a "grey'ed out" header/footer represents extra material which is

- useful and/or interesting but out of scope (and hence not covered).

| Notes. |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

| 1      |  |  |

|        |  |  |

|        |  |  |

| 1      |  |  |

|        |  |  |

|        |  |  |

| 1      |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

| Notes: |  |  |

COMS10015 lecture: week #8 + #9

► Agenda: introduce the topic [4, Part 1] of

finite automata ≡ Finite State Machines (FSMs)

via

- 1. an "in theory", i.e., concept-oriented perspective, and

- 2. an "in practice", i.e., perspective, spanning

- 2.1 general application, and

- 2.2 specific implementation in sequential logic design.

git # b282dbb9 @ 2025-09-03

Part 1: in theory (1)

#### Definition

An alphabet is a non-empty set of symbols.

#### Definition

A **string** X with respect to some alphabet  $\Sigma$  is a sequence, of finite length, whose elements are members of  $\Sigma$ , i.e.,

$$X = \langle X_0, X_1, \dots, X_{n-1} \rangle$$

for some n such that  $X_i \in \Sigma$  for  $0 \le i < n$ ; if n is zero, we term X the **empty string** and denote it  $\epsilon$ . It can be useful, and is common to write elements in in human-readable form termed a **string literal**: this basically means writing them from right-to-left without any associated notation (e.g., brackets or commas).

### Definition

A language  $\Lambda$  is a set of strings.

| Notes: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

# Part 1: in theory (2)

# Definition

A (formal) grammar is a tuple

$$G=(N,n,T,P)$$

including

- 1. N, a finite set of **non-terminal symbols** that includes a **start symbol**  $n \in N$ ,

- 2. *T*, a finite set of **terminal symbols** (which is disjoint from *N*), and

- 3. *P*, a finite set of **production rules** each of the form

$$P_i: (N \cup T)^* \to (N \cup T)^*.$$

git # b282dbb9 @ 2025-09-03

# Part 1: in theory (3)

► Concept: Finite State Machines (FSMs) are a model of computation.

| Notes: |  |

|--------|--|

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

| Notes: |  |

|        |  |

# Part 1: in theory (3)

|  | Concept: | <b>Finite</b> | State | Machines | (FSMs) | are a | model | of com | putation |

|--|----------|---------------|-------|----------|--------|-------|-------|--------|----------|

|--|----------|---------------|-------|----------|--------|-------|-------|--------|----------|

▶ An FSM is an (idealised) computer *C*, which, at a given point in time, is in one of some finite set of states.

|--|

# Part 1: in theory (3)

- ► Concept: Finite State Machines (FSMs) are a model of computation.

- ▶ An FSM is an (idealised) computer *C*, which, at a given point in time, is in one of some finite set of states.

- C accepts an input string with respect to some alphabet Σ, one symbol at a time; each symbol induces a change in state.

| 1,0 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |  |  |

|-----|-----------------------------------------|--|--|

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

| 1   |                                         |  |  |

| 1   |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

|     |                                         |  |  |

| Ne  | ntos:                                   |  |  |

| No  | otes:                                   |  |  |

| Nec | otes:                                   |  |  |

| No  | otes:                                   |  |  |

## Part 1: in theory (3)

- ► Concept: Finite State Machines (FSMs) are a model of computation.

- ► An FSM is an (idealised) computer *C*, which, at a given point in time, is in one of some finite set of states.

- ightharpoonup C accepts an input string with respect to some alphabet  $\Sigma$ , one symbol at a time; each symbol induces a change in state.

- Once the input is exhausted, *C* halts: depending on the state it halts in, we say either

- 1. *C* accepts (or recognises) the input string

- 2. *C* rejects the input string

| © Daniel Page (zsdsp@bristol.ac.uk) Computer Architecture | University of BRISTOL | git # b282dbb9 @ 2025-09-03 |

|-----------------------------------------------------------|-----------------------|-----------------------------|

|                                                           |                       |                             |

# Part 1: in theory (3)

- ► Concept: Finite State Machines (FSMs) are a model of computation.

- ► An FSM is an (idealised) computer *C*, which, at a given point in time, is in one of some finite set of states.

- ightharpoonup C accepts an input string with respect to some alphabet  $\Sigma$ , one symbol at a time; each symbol induces a change in state.

- Once the input is exhausted, *C* halts: depending on the state it halts in, we say either

- 1. *C* accepts (or recognises) the input string

- 2. *C* rejects the input string

- For a language  $\Lambda$  of all possible input strings C could accept, we say

C accepts (or recognises)  $\Lambda \equiv \Lambda$  is the language of C

and use  $\Lambda$  to classify C ...

| Notes: |

|--------|

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

# Part 1: in theory (4)

| Definition                          |                        |                                          |                                       |                                                                     |                                   |

|-------------------------------------|------------------------|------------------------------------------|---------------------------------------|---------------------------------------------------------------------|-----------------------------------|

|                                     | less powerful          |                                          |                                       |                                                                     | more powerful                     |

| Machine                             | Combinatorial<br>logic | Finite<br>automaton                      | Push-down<br>automaton                | Linear-bounded<br>automaton                                         | Turing<br>machine                 |

| Memory                              |                        | 0 stacks                                 | 1 stacks                              | 2 stacks                                                            | 2 stacks                          |

| Language                            |                        | regular                                  | context<br>free                       | context<br>sensitive                                                | recursively<br>enumerable         |

| Grammar                             |                        | regular $(X \to x \text{ or } X \to xY)$ | context free $(X \rightarrow \gamma)$ | context sensitive $(\alpha X\beta \rightarrow \alpha \gamma \beta)$ | unrestricted $(\alpha \to \beta)$ |

| Chomsky-Schützenberger<br>hierarchy |                        | type-3                                   | type-2                                | type-1                                                              | type-0                            |

| Daniel Page (csdsp@bristol.ac.uk) | University of BRISTOL |

|-----------------------------------|-----------------------|

| Computer Architecture             | S BRISTOL             |

git # b282dbb9 @ 2025-09-03

# Part 1: in theory (5)

# Definition A (deterministic) Finite State Machine (FSM) is a tuple

$C = (S, s, A, \Sigma, \Gamma, \delta, \omega)$

including

- 1. *S*, a finite set of **states** that includes a **start state**  $s \in S$ ,

- 2.  $A \subseteq S$ , a finite set of accepting states,

- 3. an **input alphabet**  $\Sigma$  and an **output alphabet**  $\Gamma$ ,

- 4. a transition function

$\delta: S \times \Sigma \to S$

and

5. an output function

$\omega:S\to\Gamma$

in the case of a Moore FSM, or

$\omega: S \times \Sigma \to \Gamma$

in the case of a Mealy FSM,

noting an **empty** input denoted  $\epsilon$  allows a transition that can *always* occur.

| lsp@bristol.ac.uk) | ® ₭ Univ |

|--------------------|----------|

| Architecture       | 🛁 🎒 BR   |

| • | In the description of grammars, the idea is (read from left-to-right) there are progressively less and less restrictions: X and Y both                     |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | represent non-terminal symbols, x represents a terminal symbol, and $\alpha$ , $\beta$ and $\gamma$ are strings of either terminal or non-terminal symbols |

|   | all with respec to some alphabet and grammar. So, the far right-hand case has rules that are totally unrestricted, for example, whereas                    |

|   | the far left-hand case has rules that must be of a particular form                                                                                         |

| Notes: |

|--------|

|--------|

• Even if the state space is *huge*, it is still finite: to cope,  $\delta$  can a **partial function** meaning it needn't be defined for all inputs.

# Part 1: in theory (6)

▶ Problem: design an FSM that decides whether a binary sequence *X* has an odd number of 1 elements in it.

| Daniel Page (csdsp@bristol.ac.uk) |  |

|-----------------------------------|--|

| Commutos Asobitostuso             |  |

University of BRISTOL

Part 1: in theory (6)

# ► Solution:

| Algorithm | (tabu                                 | ılar)                |                                       |  |

|-----------|---------------------------------------|----------------------|---------------------------------------|--|

|           | Q<br>S <sub>even</sub>                | $X_i = 0$ $S_{even}$ |                                       |  |

|           | S <sub>even</sub><br>S <sub>odd</sub> | Sodd                 | S <sub>odd</sub><br>S <sub>even</sub> |  |

# Algorithm (diagram) $X_i = 0$ $X_i = 0$ $X_i = 1$ start $X_i = 1$

# where, e.g.,

1. for the input string  $X = \langle 1, 0, 1, 1 \rangle$  the transitions are

$$\sim S_{even} \stackrel{X_0=1}{\sim} S_{odd} \stackrel{X_1=0}{\sim} S_{odd} \stackrel{X_2=1}{\sim} S_{even} \stackrel{X_3=1}{\sim} S_{odd}$$

so the input is accepted (i.e., has an odd number of 1 elements). 2. for the input string  $X = \langle 0, 1, 1, 0 \rangle$  the transitions are

$$\sim S_{even} \stackrel{X_0=0}{\sim} S_{even} \stackrel{X_1=1}{\sim} S_{odd} \stackrel{X_2=1}{\sim} S_{even} \stackrel{X_3=0}{\sim} S_{even}$$

so the input is rejected (i.e., has an even number of 1 elements).

| Notes: |  |

|--------|--|

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

| Notes: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

Example #1: regular expressions + grep → FSMs as recognisers

### ► Context:

-ve perspective:

+ve perspective: we could say that

$\begin{array}{ccc} \textbf{arithmetic expression} & \overset{evaluate}{\sim} & \text{number} \\ \textbf{regular expression} & \overset{evaluate}{\sim} & \text{language} \end{array}$

so a regular expression (or regex) can be used as

- 1. a pattern used to describe or generate a language, or

- 2. a pattern used to identify (i.e., match) members of a language.

https://xkcd.com/1171

© Daniel Page (csdsp@bristol.ac. Computer Architecture University of BRISTOL

git # b282dbb9 @ 2025-09-03

# Part 2.1: in practice, application (2)

Example #1: regular expressions + grep → FSMs as recognisers

#### Definition

We say X is a **regular expression** if it is

- 1. a symbol in the alphabet, i.e.,  $\{x\}$  for  $x \in \Sigma$ ,

- 2. the union of regular expressions *X* and *Y* such that

$$X \cup Y = \{x \mid x \in X \lor x \in Y\},\$$

3. the concatination of regular expressions X and Y such that

$$X \parallel Y = \{\langle x, y \rangle \mid x \in X \land y \in Y\},\$$

0

4. the **Kleene star** of regular expression *X* such that

$$X^* = \{ \langle x_0, x_1, \dots, x_{n-1} \rangle \mid n \ge 0, x_i \in X \}.$$

allowing for various short-hands, e.g.,

$$\begin{array}{rcl}

x & \equiv & \{x\} \\

xy & \equiv & \{x\} \parallel \{y\} \\

X^+ & \equiv & X \parallel X^*

\end{array}$$

# b282dbb9 @ 2025-09-03

| Notes: |  |

|--------|--|

| Title. |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

| Notes: |  |

Example #1: regular expressions + grep → FSMs as recognisers

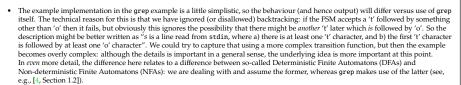

**Example** [4, Example 1.53]: if  $\Sigma = \{0, 1\}$ , then

$$0^*10^* \equiv \left\{ \begin{array}{c|c} s & \text{s is a string containing} \\ a & \text{single 1} \end{array} \right\}$$

© Daniel Page (csdsp@bristol.ac.u Computer Architecture University of BRISTOL

git # b282dbb9 @ 2025-09-03

# Part 2.1: in practice, application (3)

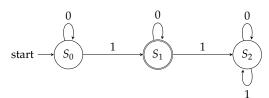

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{0, 1\}$ , then

$$0^*10^* \equiv \left\{ \begin{array}{c} s \mid s \text{ is a string containing} \\ a \text{ single 1} \end{array} \right\}$$

which can be realised using

© Daniel Page (csdsp@bristol.ac.ul Computer Architecture

Note

| - 1 | Notes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | • The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 't' followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as "s is a line read from stdin, where a) there is at least one 't' character, and b) the first 't' character is followed by at least one 'o' character". We could try to capture that using a more complex transition function, but then the example becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]). |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Notes:

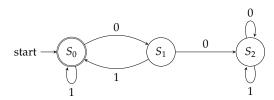

• The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 'Y followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as "s is a line read from stdin, where a) there is at least one 't' character, and b) the first 't' character is followed by at least one 'o' character". We could try to capture that using a more complex transition function, but then the example becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]).

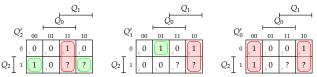

#### Part 2.1: in practice, application (3) Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{0, 1\}$ , then

$$\Sigma^*001\Sigma^* \equiv \left\{ \begin{array}{c} s \mid s \text{ is a string containing} \\ 001 \text{ as a sub-string} \end{array} \right\}$$

which can be realised using

University of BRISTOL

# Part 2.1: in practice, application (3)

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{0, 1\}$ , then

$$\Sigma^* 001\Sigma^* \equiv \left\{ \begin{array}{c} s \mid s \text{ is a string containing} \\ 001 \text{ as a sub-string} \end{array} \right\}$$

which can be realised using

| o | tes:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 't' followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as "s is a line read from stdin, where a) there is at least one 't' character, and b) the first 't' character is followed by at least one 'o' character'. We could try to capture that using a more complex transition function, but then the example becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]). |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

. The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 't' followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as "s is a line read from stdin, where a) there is at least one 't' character, and b) the first 't' character is followed by at least one 'o' character". We could try to capture that using a more complex transition function, but then the example becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]).

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{0, 1\}$ , then

$$(\Sigma \Sigma)^* \equiv \left\{ \begin{array}{c} s \text{ is a string} \\ \text{of even length} \end{array} \right\}$$

© Daniel Page (csdsp@bristol.ac.uk)

Computer Architecture

University of BRISTOL

git # b282dbb9 @ 2025-09-03

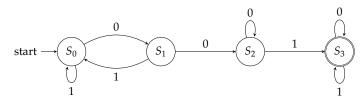

# Part 2.1: in practice, application (3)

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{0, 1\}$ , then

$$(\Sigma \Sigma)^* \equiv \left\{ \begin{array}{c} s \mid s \text{ is a string} \\ \text{of even length} \end{array} \right\}$$

which can be realised using

#### Notes:

#### Notes:

• The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 't' followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as "s is a line read from stdin, where a) there is at least one 'd' character, and b) the first 't' character is followed by at least one 'o' character". We could try to capture that using a more complex transition function, but then the example becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]).

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{0, 1\}$ , then

$$1^*(01^+)^* \equiv \left\{ s \mid s \text{ is a string in which every 0 is followed by at least one 1} \right\}$$

© Daniel Page (csdsp@bristol.ac.

University of BRISTOL

git # b282dbb9 @ 2025-09-0

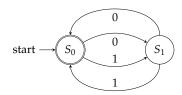

# Part 2.1: in practice, application (3)

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{0, 1\}$ , then

$$1^*(01^+)^* \equiv \left\{ s \mid \begin{array}{c} s \text{ is a string in which} \\ \text{every } 0 \text{ is followed by at least one } 1 \end{array} \right\}$$

which can be realised using

Daniel Page (csdsp@bristol.ac.uk)

Computer Architecture

#### Notes:

| • | The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 't' followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as "s is a line read from stdin, where a) there is at least one 'o' character, and b) the first 't' character is followed by at least one 'o' character". We could try to capture that using a more complex transition function, but then the example |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]).                                                                                                                                                                                                                                                                                                    |

#### Notes:

• The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 't' followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as 's is a line read from stdin, where a) there is at least one 't' character, and b) the first 't' character is followed by at least one 'o' character". We could try to capture that using a more complex transition function, but then the example becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]).

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{ (a', b', \dots, z') \}$ , then

grep -E '.\*to+.\*'

$$\equiv \left\{ s \mid s \text{ is a line read from stdin containing a 't' followed by at least one 'o' character} \right\}$$

© Daniel Page (csdsp@bristol.ac.

University of BRISTOL

git # b282dbb9 @ 2025-09-0

# Part 2.1: in practice, application (3)

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{'a', 'b', \dots, 'z'\}$ , then

grep -E '.\*to+.\*'

$$\equiv \left\{ s \mid s \text{ is a line read from stdin containing a 't' followed by at least one 'o' character} \right\}$$

which can be realised using

© Daniel Page (csdsp@bristol.a Computer Architecture

#### Notes:

#### Notes:

• The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 't' followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as "s is a line read from stdin, where a) there is at least one 'd' character, and b) the first 't' character is followed by at least one 'o' character". We could try to capture that using a more complex transition function, but then the example becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]).

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{'a', 'b', \ldots, 'z'\}$ , then

grep -E '.\*to+.\*'

$$\equiv \left\{ s \mid s \text{ is a line read from stdin containing } a \text{ 't' followed by at least one 'o' character} \right\}$$

which can be realised using

```

1 forall lines X read from stdin do

for i = 0 upto n - 1 do

Q \leftarrow \delta(Q, X_i)

if Q \in A then

print line X to stdout

10

11 end

```

University of BRISTOL

# Part 2.1: in practice, application (3)

Example #1: regular expressions + grep → FSMs as recognisers

**Example** [4, Example 1.53]: if  $\Sigma = \{ 'a', 'b', ..., 'z' \}$ , then

grep -E '.\*to+.\*'

$$\equiv \left\{ s \mid s \text{ is a line read from stdin containing a 't' followed by at least one 'o' character} \right\}$$

which can be realised using

```

void grep() {

char X[ 1024 ];

while( NULL != fgets( X, 1024, stdin ) ) {

int n = strlen( X ), Q = start;

if( X[ n - 1 ] == '\n' ) {

X[n-1] = '\0'; n--;

for( int i = 0; i < n; i++ ) {

Q = delta[ Q ][ X[ i ] ];

if( accept[ Q ] ) {

fprintf( stdout, "%s\n", X );

18 }

19 }

```

#### Notes:

| • | The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 't' followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as "s is a line read from stdin, where a) there is at least one 'o' character, and b) the first 't' character is followed by at least one 'o' character". We could try to capture that using a more complex transition function, but then the example |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]).                                                                                                                                                                                                                                                                                                    |

. The example implementation in the grep example is a little simplistic, so the behaviour (and hence output) will differ versus use of grep itself. The technical reason for this is that we have ignored (or disallowed) backtracking: if the FSM accepts a 't' followed by something other than 'o' then it fails, but obviously this ignores the possibility that there might be another 't' later which is followed by 'o'. So the description might be better written as "s is a line read from stdin, where a) there is at least one 't' character, and b) the first 't' character is followed by at least one 'o' character". We could try to capture that using a more complex transition function, but then the example becomes overly complex: although the details is important in a general sense, the underlying idea is more important at this point. In even more detail, the difference here relates to a difference between so-called Deterministic Finite Automatons (DFAs) and Non-deterministic Finite Automatons (NFAs): we are dealing with and assume the former, whereas grep makes use of the latter (see, e.g., [4, Section 1.2]).

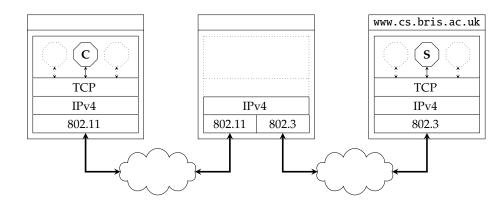

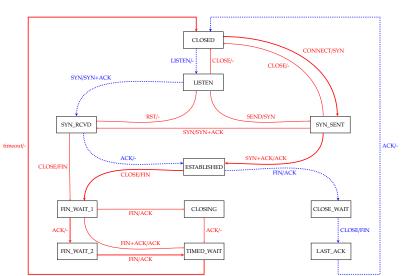

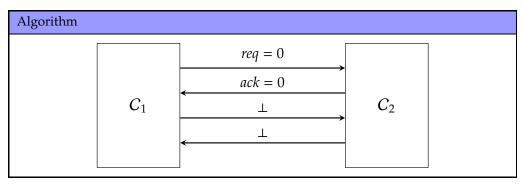

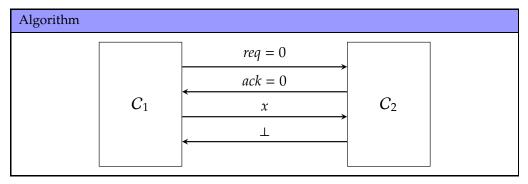

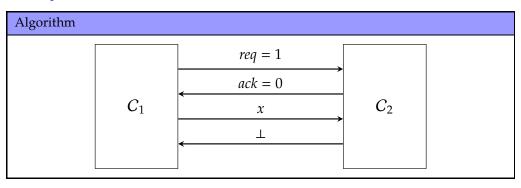

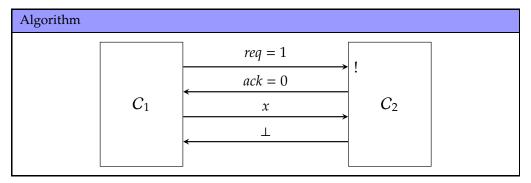

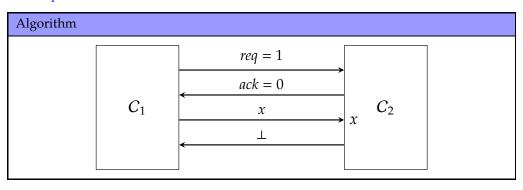

# Part 2.1: in practice, application (4) Example #2: networked communication via TCP $\leadsto$ FSMs as controllers

### ► Context:

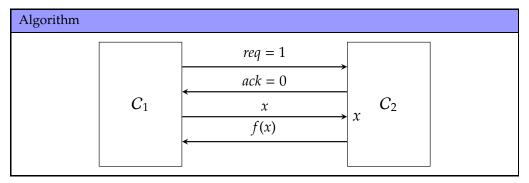

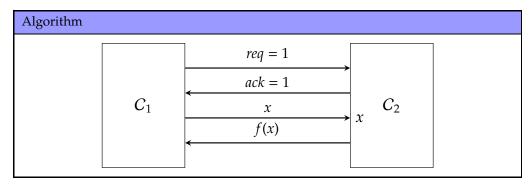

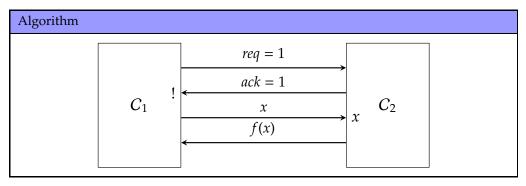

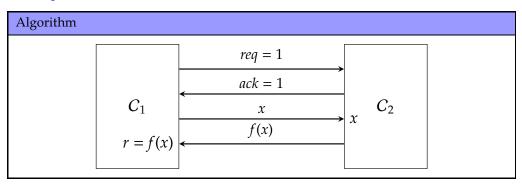

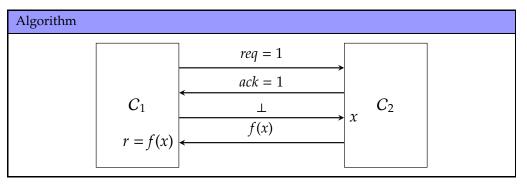

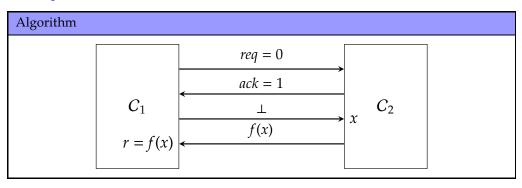

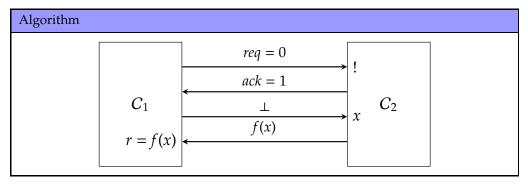

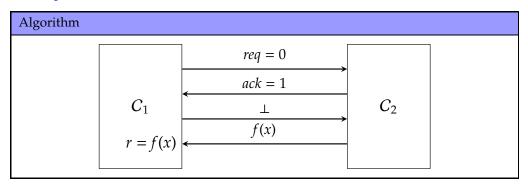

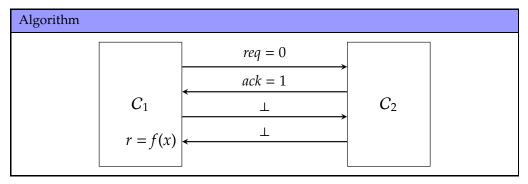

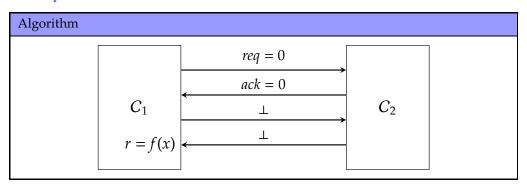

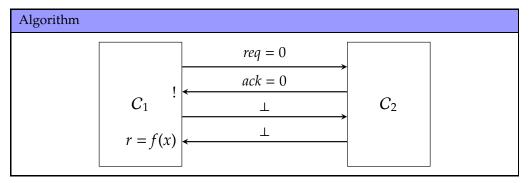

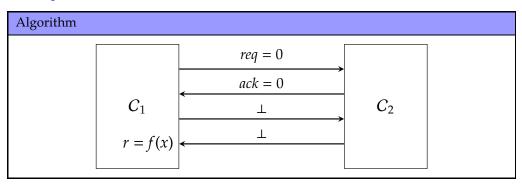

Part 2.1: in practice, application (5)

Example #2: networked communication via TCP → FSMs as controllers

# **Example:**

# Part 2.1: in practice, application (6) Example #3: typical video game "loop" → FSMs as systems

## ► Context:

# Algorithm

- reset the game state

while ¬ game over do

- read control pad (e.g., check if button pressed) update game state (e.g., move player) produce graphics and/or sound

© Daniel Page (csdsp@bristol. Computer Architecture

University of BRISTOL

Part 2.1: in practice, application (6)

Example #3: typical video game "loop" → FSMs as systems

### ► Context:

# Algorithm

1  $Q \leftarrow s$

while  $Q \notin A$  do  $X_i \leftarrow \text{control pad}$   $Q \leftarrow \delta(Q, X_i)$

$\{\text{graphics, sound}\} \leftarrow \omega(Q)$

6 end

| Notes: |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

| Notes: |

|--------|

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

# Part 2.1: in practice, application (7) Example #3: typical video game "loop" → FSMs as systems

# **Example:**

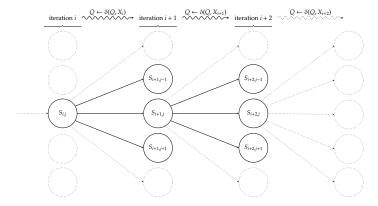

$\begin{array}{ccc} \text{iterations of game loop} & \leadsto & \text{game tree} \\ & \simeq & \text{state space} \end{array}$

i.e.,

which is most obvious with respect to turn-based games (e.g., chess).

© Daniel Page (cdspthristol.acm.)

Computer Architecture

© Daniel Page (cdspthristol.acm.)

EM University of

BRISTOL git # b282dbb9 @ 2025-09-00

Part 2.2: in practice, implementation (1) Design framework

#### ► Recall:

#### Definition

A (deterministic) Finite State Machine (FSM) is a tuple

$$C = (S, s, A, \Sigma, \Gamma, \delta, \omega)$$

including

- 1. S, a finite set of **states** that includes a **start state**  $s \in S$ ,

- 2.  $A \subseteq S$ , a finite set of accepting states,

- 3. an **input alphabet**  $\Sigma$  and an **output alphabet**  $\Gamma$ ,

- 4. a transition function

$\delta: S \times \Sigma \to S$

and

5. an output function

$\omega:S\to\Gamma$

in the case of a Moore FSM, or

$\omega: S \times \Sigma \to \Gamma$

in the case of a Mealy FSM,

noting an **empty** input denoted  $\epsilon$  allows a transition that can *always* occur.

| Notes: |      |

|--------|------|

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        | <br> |

| Notes: |      |

|        |      |

|        |      |

|        |      |

|        |      |

|        |      |

| Notes: |

|--------|

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

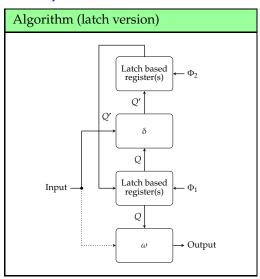

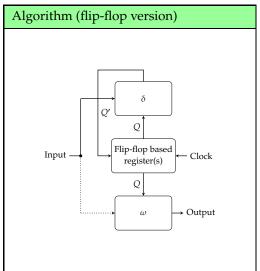

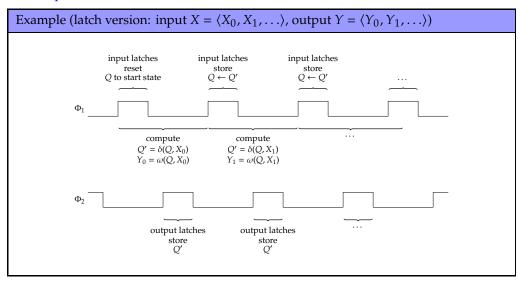

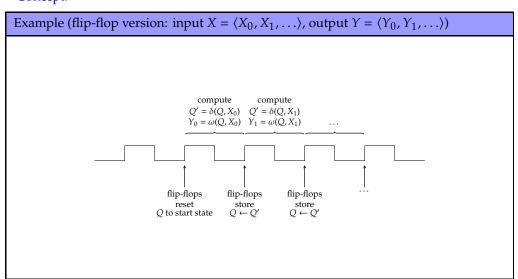

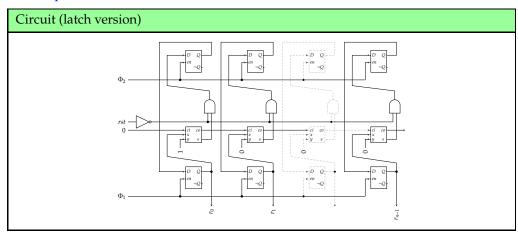

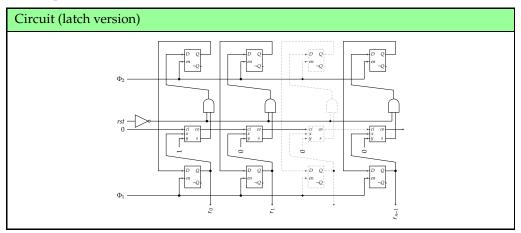

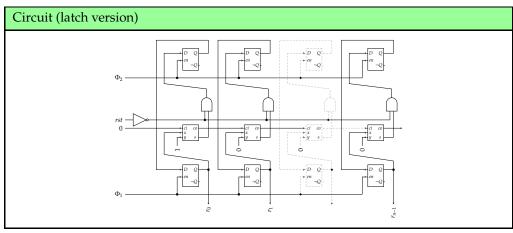

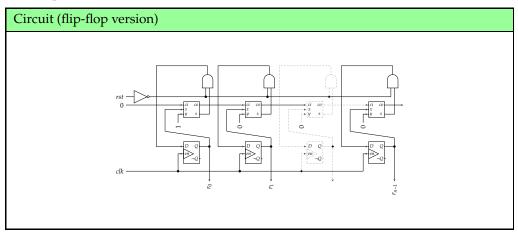

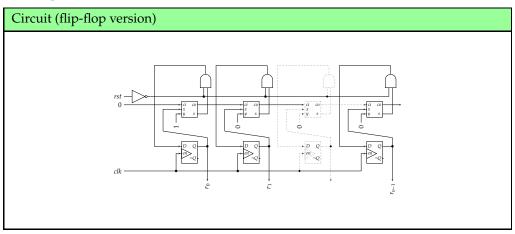

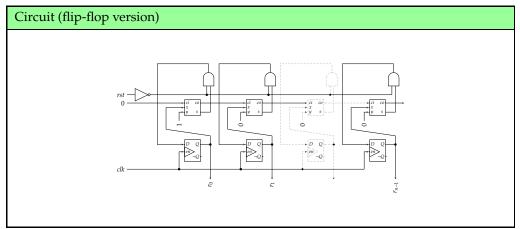

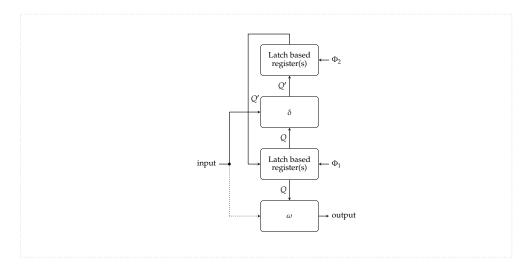

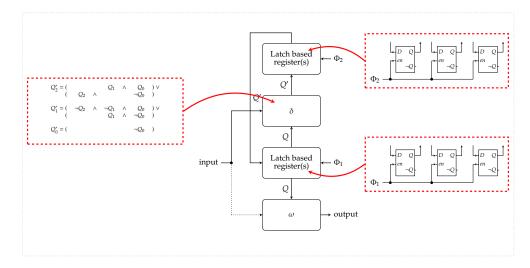

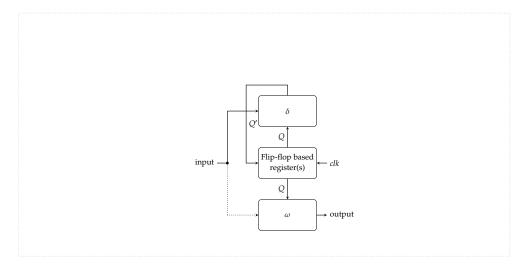

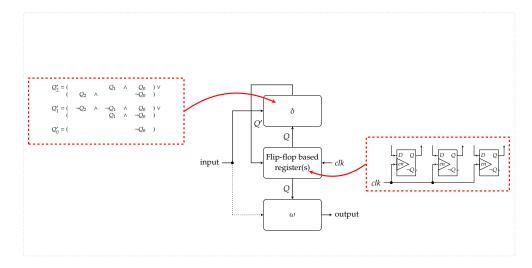

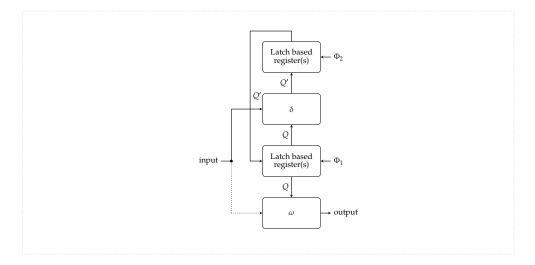

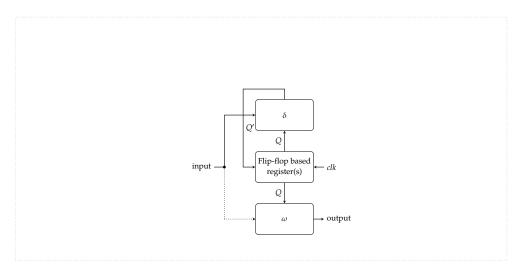

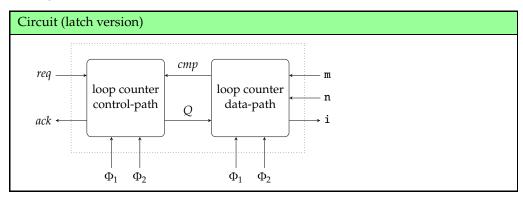

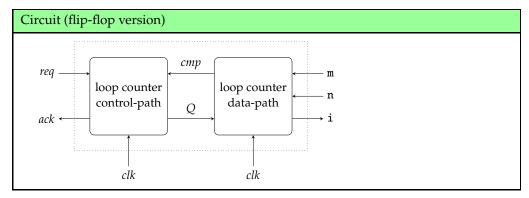

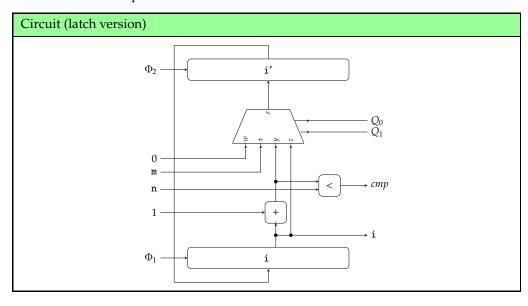

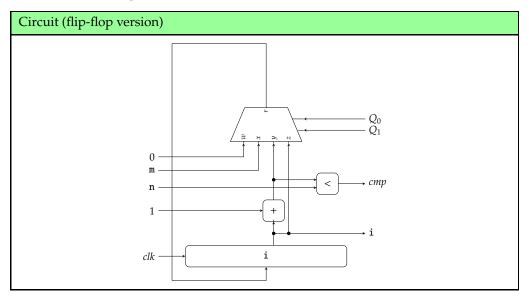

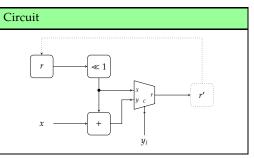

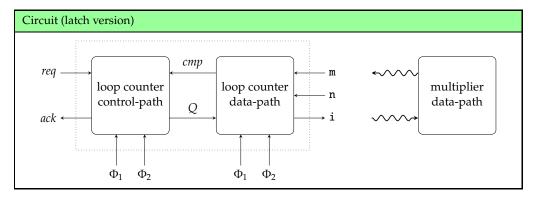

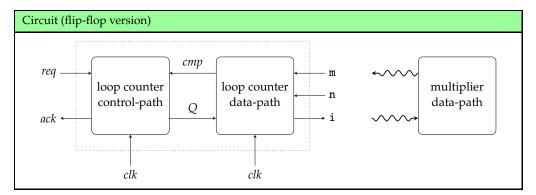

# Part 2.2: in practice, implementation (2) Design framework

## ► Concept:

#### Note that

- 1. the state is retained in a register (i.e., a group of latches, resp. flip-flops),

- 2.  $\delta$  and  $\omega$  are simply combinatorial logic,

- 3. within the current clock cycle

- $\omega$  computes the output from the current state and input, and

- $\delta$  computes the next state from the current state and input,

- 4. the next state is latched by an appropriate feature (i.e., level, resp. edge) in the clock

i.e., it's a *computer* we can *build*!

© Daniel Page (-sdspibristol.ac.uk)

Computer Architecture

© BRISTOL

git # b282dbb9 @ 2025-09-03

Part 2.2: in practice, implementation (3) Design framework

# ► Concept:

- Note that

- 1. the state is retained in a register (i.e., a group of latches, resp. flip-flops),

- 2.  $\delta$  and  $\omega$  are simply combinatorial logic,

- 3. within the current clock cycle

- $oldsymbol{\omega}$  computes the output from the current state and input, and

- $\delta$  computes the next state from the current state and input,

- 4. the next state is latched by an appropriate feature (i.e., level, resp. edge) in the clock

i.e., it's a computer we can build!

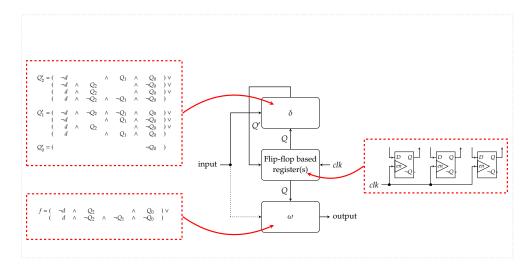

# Part 2.2: in practice, implementation (4) Design framework

# ► Concept:

Part 2.2: in practice, implementation (5)

Design framework

# ► Concept:

# Part 2.2: in practice, implementation (6) Design framework

► Concept: this *should* sound familar, because from

it now becomes clear that

- ▶  $2^n$  states, labelled  $S_0$  through  $S_{2^n-1}$ ; state  $S_i$  represented as (unsigned) n-bit integer i, the start state is  $s = S_0$  and there are no accepting states (so  $A = \emptyset$ ),

► Concept: this *should* sound familar, because from

it now becomes clear that

• the  $\delta$  function is

$$Q' \leftarrow \delta(Q, rst) = \begin{cases} Q+1 \pmod{2^n} & \text{if } rst = 0\\ 0 & \text{if } rst = 1 \end{cases}$$

# Part 2.2: in practice, implementation (6) Design framework

► Concept: this *should* sound familar, because from

it now becomes clear that

• the  $\omega$  function is  $r \leftarrow \omega(Q) = Q$ .

Part 2.2: in practice, implementation (7) Design framework

► Concept: this *should* sound familar, because from

it now becomes clear that

- 2<sup>n</sup> states, labelled S<sub>0</sub> through S<sub>2<sup>n</sup>-1</sub>; state S<sub>i</sub> represented as (unsigned) *n*-bit integer *i*,

the start state is s = S<sub>0</sub> and there are no accepting states (so A = ∅),

# Part 2.2: in practice, implementation (7) Design framework

► Concept: this *should* sound familar, because from

it now becomes clear that

• the  $\delta$  function is

$$Q' \leftarrow \delta(Q, rst) = \begin{cases} Q+1 \pmod{2^n} & \text{if } rst = 0\\ 0 & \text{if } rst = 1 \end{cases}$$

Computer Architecture

University of BRISTOL

git # b282dbb9 @ 2025-09-03

Part 2.2: in practice, implementation (7) Design framework

► Concept: this *should* sound familar, because from

it now becomes clear that

• the  $\omega$  function is  $r \leftarrow \omega(Q) = Q$ .

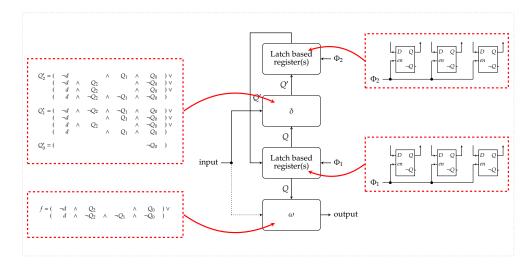

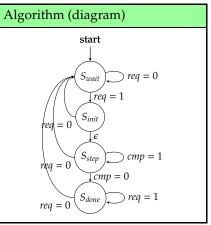

# Part 2.2: in practice, implementation (8) Design process

▶ Concept to solve a concrete problem, we follow a (fairly) standard sequence of steps

# Algorithm

- 1. Count the number of states required, and give each state an abstract label.

- 2. Describe the state transition and output functions using a tabular or diagrammatic approach.

- 3. Perform state assignment, i.e., decide how concrete values will represent the abstract labels, allocating appropriate register(s) to hold the state.

- 4. Express the functions  $\delta$  and  $\omega$  as (optimised) Boolean expressions, i.e., combinatorial logic.

- 5. Place the registers and combinatorial logic into the framework.

### noting that it's common to

- include a **reset** input that (re)initialises the FSM into the start state,

- replace the accepting state(s) with an idle or error state since "halting" doesn't make sense in hardware, and

- use the FSM to control an associated data-path using the outputs, rather than (necessarily) solve some problem outright.

| © Daniel Page (csdsp@bristol.ac.uk) Computer Architecture | University of BRISTOL |  |

|-----------------------------------------------------------|-----------------------|--|

|                                                           |                       |  |

git # b282dbb9 @ 2025-09-

# Part 2.2: in practice, implementation (9) Design process

- ▶ Concept: we can optimise the state representation based on use of it, e.g.,

- 1. a **binary encoding** represents the *i*-th of *n* states as a ( $\lceil \log_2(n) \rceil$ )-bit unsigned integer *i*, e.g.,

$$\begin{array}{cccc} S_{0} & \mapsto & \langle 0, 0, 0 \rangle \\ S_{1} & \mapsto & \langle 1, 0, 0 \rangle \\ S_{2} & \mapsto & \langle 0, 1, 0 \rangle \\ S_{3} & \mapsto & \langle 1, 1, 0 \rangle \\ S_{4} & \mapsto & \langle 0, 0, 1 \rangle \\ S_{5} & \mapsto & \langle 1, 0, 1 \rangle \end{array}$$

2. a **one-hot encoding** represents the *i*-th of *n* states as a sequence *X* such that  $X_i = 1$  and  $X_j = 0$  for  $j \neq i$ , e.g.,

$$\begin{array}{cccc} S_0 & \mapsto & \langle 1,0,0,0,0,0,0 \rangle \\ S_1 & \mapsto & \langle 0,1,0,0,0,0,0 \rangle \\ S_2 & \mapsto & \langle 0,0,1,0,0,0 \rangle \\ S_3 & \mapsto & \langle 0,0,0,1,0,0 \rangle \\ S_4 & \mapsto & \langle 0,0,0,0,1,0 \rangle \\ S_5 & \mapsto & \langle 0,0,0,0,0,1,1 \rangle \end{array}$$

noting that we have a larger state (i.e., n bits instead of  $\lceil \log_2(n) \rceil$ ), but

- transition between states is easier, and

- switching behaviour (and hence power consumption) is reduced.

| Notes:  |   |

|---------|---|

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

|         |   |

| Materia | 1 |

| Notes:  | ] |

| Notes:  |   |

| Notes:  |   |

| Notes:  | 7 |

| Notes:  |   |

| Notes:  | 7 |

| Notes:  |   |

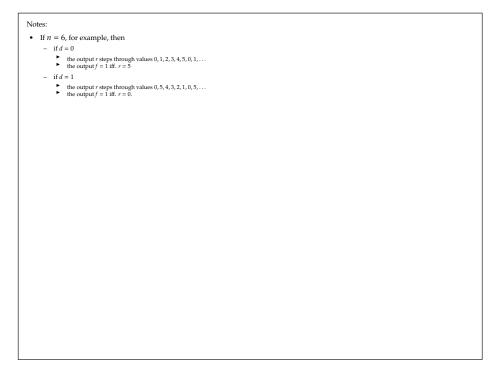

### Part 2.2: in practice, implementation (10) Example #1: a modulo 6 ascending counter

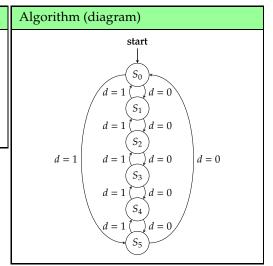

**Problem:** design an FSM that acts as a cyclic counter modulo n = 6 (versus  $2^n$ ).

Part 2.2: in practice, implementation (10)

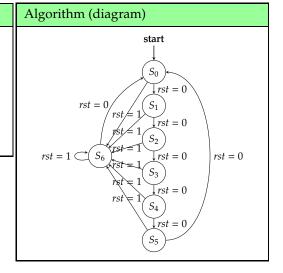

Example #1: a modulo 6 ascending counter

### ► Solution:

| Algorithm (tabular)                                    | Algorithm (diagram)                                                                                                                                                                                                |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | start $ \begin{array}{c} S_0 \\ \downarrow \varepsilon \\ S_1 \\ \downarrow \varepsilon \\ S_2 \\ \downarrow \varepsilon \\ S_3 \\ \downarrow \varepsilon \\ S_4 \\ \downarrow \varepsilon \\ S_5 \\ \end{array} $ |

| <b>1</b> K | University |

|------------|------------|

Notes:

• If n = 6 for example, then we want a component whose output r steps through values

with the modular reduction representing control behaviour (versus the uncontrolled counter that was cyclic by default).

• If n = 6 for example, then we want a component whose output r steps through values

Example #1: a modulo 6 ascending counter

### ► Solution:

there are 6 abstract labels

$$\begin{array}{cccc} S_0 & \mapsto & 0 \\ S_1 & \mapsto & 1 \\ S_2 & \mapsto & 2 \\ S_3 & \mapsto & 3 \\ S_4 & \mapsto & 4 \\ S_5 & \mapsto & 5 \end{array}$$

we can represent using 6 concrete values, e.g.,

$$\begin{array}{ccccc} S_0 & \mapsto & \langle 0,0,0 \rangle & \equiv & 000_{(2)} \\ S_1 & \mapsto & \langle 1,0,0 \rangle & \equiv & 001_{(2)} \\ S_2 & \mapsto & \langle 0,1,0 \rangle & \equiv & 010_{(2)} \\ S_3 & \mapsto & \langle 1,1,0 \rangle & \equiv & 011_{(2)} \\ S_4 & \mapsto & \langle 0,0,1 \rangle & \equiv & 100_{(2)} \\ S_5 & \mapsto & \langle 1,0,1 \rangle & \equiv & 101_{(2)} \end{array}$$

ightharpoonup since  $2^3 = 8 > 6$ , we can capture each of

1.

$$Q = \langle Q_0, Q_1, Q_2 \rangle \equiv$$

the current state

2.  $Q' = \langle Q'_0, Q'_1, Q'_2 \rangle \equiv$  the next state

in a 3-bit register (i.e., via 3 latches or flip-flops).

University of BRISTOL

git # b282dbb9 @ 2025-09-0

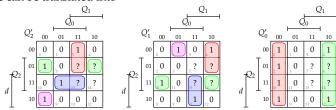

Part 2.2: in practice, implementation (10)

Example #1: a modulo 6 ascending counter

### ► Solution:

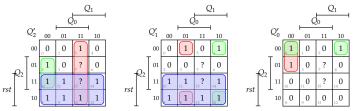

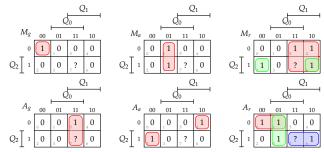

rewriting the abstract labels yields the following concrete truth table

|       |       |       |        | δ      |        |       | $\omega$ |       |

|-------|-------|-------|--------|--------|--------|-------|----------|-------|

| $Q_2$ | $Q_1$ | $Q_0$ | $Q_2'$ | $Q_1'$ | $Q_0'$ | $r_2$ | $r_1$    | $r_0$ |